What we <u>really</u> want is **True Single-Phase Clocked (TSPC) Logic** in which we only have <u>one clock</u>, and <u>do not</u> need an inverted clock.

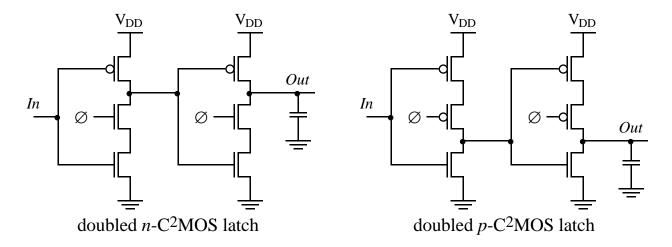

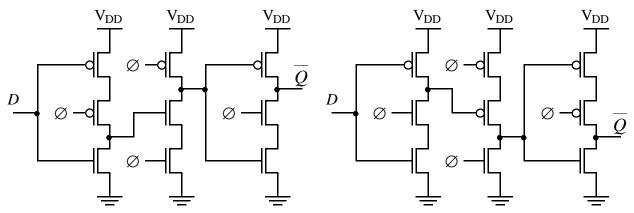

Redesign  $C^2MOS$  latch and create the **doubled** n- $C^2MOS$  latch and the **doubled** p- $C^2MOS$  latch

Doubling of the latch ensures that signal cannot propagate from input to output when latch is in hold mode (n-C<sup>2</sup>MOS latch  $\emptyset = 0$ , p-C<sup>2</sup>MOS latch  $\emptyset = 1$ )

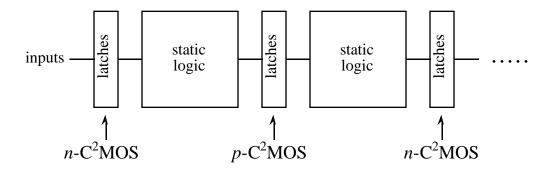

How do I make a pipelined system using these latches?

EE 4253/6253 Lecture Notes November 16, 1998 page 151

### Can also include logic into the TSPC latches!

PUN - pullup network, PDN - pulldown network, logic directly implemented in the <u>latch</u>.

No requirements on inversion of static logic between latches.

This design method was the style of choice for the (original) DEC Alpha microprocessor, which ran at 200MHz in 0.75µm CMOS technology.

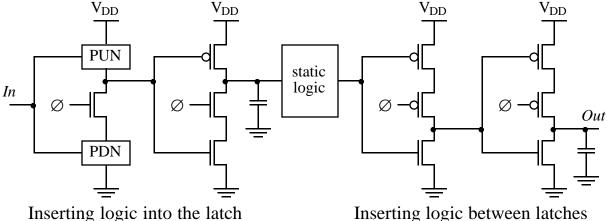

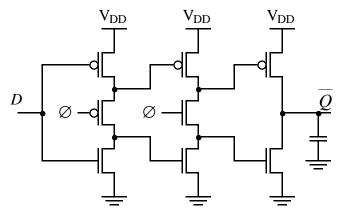

Other improvements - Simplified TSPC latch (split output latch)

Reduces transistor count by two, cuts clock load in half at the cost of reduced voltage swings on internal nodes (lowers the noise margin)

EE 4253/6253 Lecture Notes November 16, 1998 page 152

## Creating D-flip flops out of TSPC latches

Positive edge-triggered D flip-flop

Negative edge-triggered D flip-flop

Positive edge-triggered D flip-flop using split-output latches

Dynamic latches (and dynamic logic, to be discussed later) is currently the principle design style for high speed digital circuits

Question: In CMOS, with edge-triggered storage elements, would we want negative edge-triggered or positive edge-triggered?

Typically, want the clock edges as  $\underline{\text{sharp}}$  as  $\underline{\text{possible}}$ . Because nMOS devices provide stronger pulldown, usually use negative edge-triggered devices in CMOS.

EE 4253/6253 Lecture Notes November 16, 1998 page 153

# The C<sup>2</sup>MOS latch, doubled n-C<sup>2</sup>MOS, and doubled p-C<sup>2</sup>MOS latches all require sharp clock edges for correct operation.

In the DEC Alpha case, clock rise and fall times below 0.8ns caused no failures while above 1.0ns caused failures. A value of 0.5ns was set as the target for clock rise/fall.

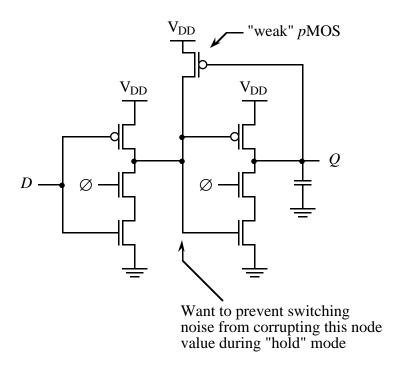

To reduce noise susceptibility, can also add a feedback transistor:

Feedback transistor sharpens output edges, reduces susceptibility to noise

When Q goes  $1 \rightarrow 0$ , feedback sharpens (speeds up) transistion

When Q = 0, helps hold 0 value by keeping p-device on (internal node at  $V_{DD}$ )

When Q goes  $0 \to 1$ , feedback transistor will act against this transistion but will be overdriven by stronger pulldown in front stage

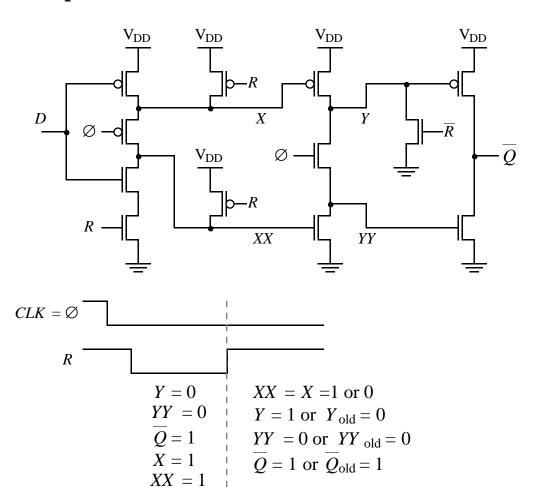

## How to add reset (asynchronous), low true

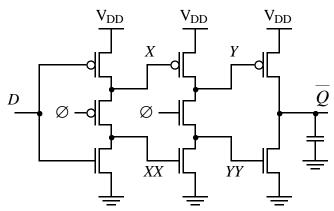

Positive edge-triggered TSPC Split Ouput D-flip flop (revisited for this example)

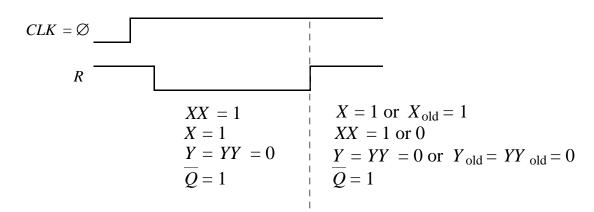

When clock = 0,  $X = XX = \overline{D}$ , YY = 0 or  $YY_{old}$ , Y = 1 or  $Y_{old}$ .

For **reset** we want  $YY = YY_{\text{old}} = 0$ ,  $\rightarrow \overline{Q} = 1$

| clock | D | X = XX | Y                    | Y Y                                         | $\overline{\overline{\mathcal{Q}}}$ |

|-------|---|--------|----------------------|---------------------------------------------|-------------------------------------|

| 0     | 0 | 1      | $Y_{\text{old}} = 0$ | 0                                           | 1                                   |

|       |   |        | = 1                  | 0                                           | $\overline{Q}_{ m old}$             |

| 0     | 1 | 0      | <i>Y</i> = 1         | $YY_{\text{old}} = 0$                       | $\overline{Q}_{ m old}$             |

|       |   |        |                      | $YY_{\text{old}} = 0$ $YY_{\text{old}} = 1$ | 0                                   |

With clock = 0, to reset correctly must affect both Y or YY.

Similarly, with clock = 1, a reset operation must affect both X or XX.

EE 4253/6253 Lecture Notes November 16, 1998 page 155

#### **Split Output Reset**

Final transistor count = 12. Recall that a static D-flip flop can require 33 transistors!

For **practice**, <u>everybody</u> is to add asynchronous, low true reset to the other two TPSC *D*-flip flops (you are doing one of these in lab anyway).