# EEL 5722C Field-Programmable Gate Array Design

Lecture 14: Introduction to SystemC\*

Prof. Mingjie Lin

#### **Outline**

- Needed tools

- Starting example

- Introduction

- SystemC highlights

- Differences

- Modules, processes, ports, signals, clocks and data types

#### **Needed tools**

- SystemC library package v2.0.1

Download in <u>www.systemc.org</u>

- Linux platform

- GCC compiler

- GTKWave Waveform tool

- some text editor

# Install SystemC

See Course Webpage

# Starting Example: Full Adder

#### FullAdder.h

```

SC_MODULE( FullAdder ) {

sc in < sc uint < 16> > A;

sc_in < sc_uint < 16 > > B;

sc_out< sc_uint<17> > result;

void dolt( void );

SC CTOR(FullAdder) {

SC METHOD( dolt );

sensitive << A:

sensitive << B;

```

#### FullAdder.cpp

```

void FullAdder::dolt( void ) {

sc_int<16> tmp_A, tmp_B;

sc_int<17> tmp_R;

tmp_A = (sc_int<16>) A.read();

tmp_B = (sc_int<16>) B.read();

tmp_R = tmp_A + tmp_B;

result.write( (sc_uint<16>) tmp_R.range(15,0) );

}

```

## Introduction

- What is SystemC?

- SystemC is a C++ class library and methodology that can effectively be used to create a cycleaccurate model of a system consisting of software, hardware and their interfaces.

#### Introduction

- Where can I use SystemC?

- In creating an executable specification of the system to be developed.

- What should I know to learn SystemC?

- Notions of C++ programming and VHDL helps you a lot.

# SystemC highlights

- Supports hardware and software co-design

- Developing an executable specification avoids inconsistency and errors

- Avoids wrong interpretation of the specification

- SystemC has a rich set of data types for you to model your systems

- It allows multiple abstraction levels, from high level design down to cycle-accurate RTL level

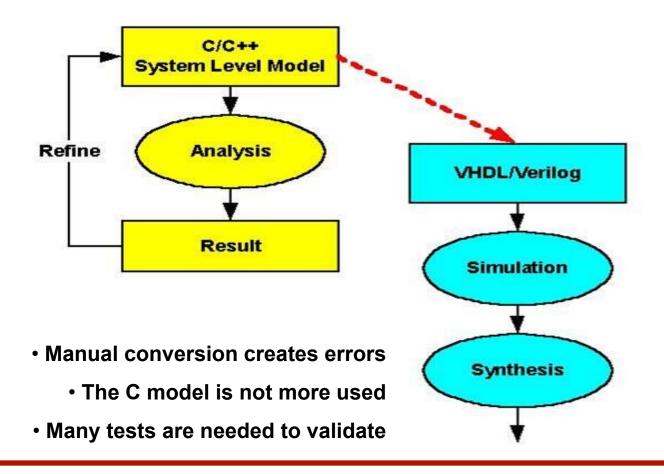

# Why is SystemC different?

Current design methodology

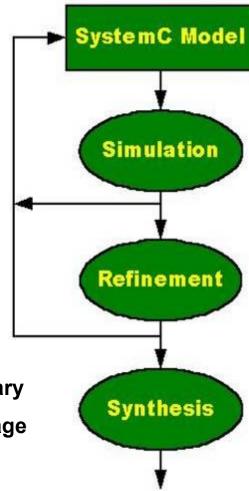

# Why is SystemC different?

SystemC design methodology

Better methodology, translate is not necessaryWritten in only one language

- Modules are the basic building blocks to partition a design

- Modules allow to partition complex systems in smaller components

- Modules hide internal data representation, use interfaces

- Modules are classes in C++

- Modules are similar to "entity" in VHDL

```

$C_MODULE(module_name)

{

// Ports declaration

// Signals declaration

// Module constructor : SC_CTOR

// Process constructors and sensibility list

// SC_METHOD

// Sub-Modules creation and port mappings

// Signals initialization

}

```

They can contain ports, signals, local data, other modules, processes and constructors.

- Module constructor

- Similar to "architecture" in VHDL

Example: Full Adder constructor

```

SC_CTOR( FullAdder ) {

SC_METHOD( doIt );

sensitive << A;

sensitive << B;

}

```

- Sub-modules instantiation:

- Instantiate module

```

Module_type Inst_module ("label");

```

• Instantiate module as a pointer

```

Module_type *pInst_module;

// Instantiate at the module constructor SC_CTOR

pInst_module = new module_type ("label");

```

## How to connect sub-modules ?

- Named Connection or

- Positional Connection

Named Connection

```

Inst_module.a(s);

Inst_module.b(c);

Inst_module.q(q);

pInst_module -> a(s);

pInst_module -> b(c);

pInst_module -> q(q);

```

Positional Connection

Inst\_module

$$<< s << c << q;$$

$(*pInst_module)(s,c,q);$

- Internal Data Storage

- Local variables: can not be used to connect ports

- Allowed data types

- C++ types

- SystemC types

- User defined types

• Example: Mux 2:1

```

SC_MODULE( Mux21 ) {

sc_in < sc_uint < 8 > in 1;

sc_in< sc_uint<8> > in2;

sc_in< bool >

selection;

sc_out< sc_uint<8> > out;

void doIt( void );

SC_CTOR( Mux21 ) {

SC_METHOD( doIt );

sensitive << selection;

sensitive << in1;

sensitive << in2;

};

```

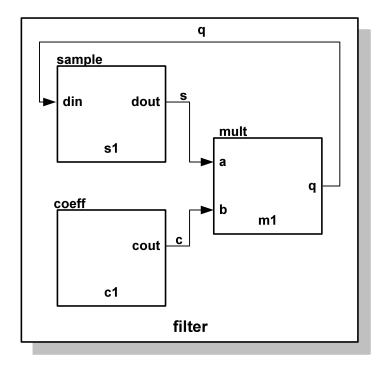

#### • Example:

```

SC_MODULE(filter) {

// Sub-modules : "components"

sample *s1;

coeff *c1;

mult *m1;

sc_signal<sc_uint 32> > q, s, c; // Signals

// Constructor: "architecture"

SC_CTOR(filter) {

// Sub-modules instantiation and

mapping

s1 = new sample ("s1");

s1->din(q); // named mapping

s1->dout(s);

c1 = new coeff("c1");

c1->out(c); // named mapping

m1 = new mult ("m1");

(*m1)(s, c, q); // Positional mapping

}

}

```

- Processes are functions that are identified to the SystemC kernel. They are called if one signal of the sensitivity list changes its value.

- Processes implement the functionality of modules

- Processes are very similar to a C++ function or method

- Processes can be Methods, Threads and CThreads

#### Methods

When activated, executes and returns

SC\_METHOD(process\_name)

#### Threads

Can be suspended and reactivated

- wait() -> suspends

- one sensitivity list event -> activates

- SC\_THREAD(process\_name)

#### CThreads

Are activated in the clock pulse

- SC\_CTHREAD(process\_name, clock value);

| Туре                                        | SC_METHOD                                                                                 | SC_THREAD                                                                                 | SC_CTHREAD                                                                |

|---------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Activates Exe<br>c.                         | Event in sensit. list                                                                     | Event in sensit. List                                                                     | Clock pulse                                                               |

| Suspends Exe<br>c.                          | NO                                                                                        | YES                                                                                       | YES                                                                       |

| Infinite Loop                               | NO                                                                                        | YES                                                                                       | YES                                                                       |

| suspended/ r<br>eactivated by               | N.D.                                                                                      | wait()                                                                                    | wait()<br>wait_until()                                                    |

| Constructor &<br>Sensibility def<br>inition | SC_METHOD(call_back); sensitive(signals); sensitive_pos(signals); sensitive_neg(signals); | SC_THREAD(call_back); sensitive(signals); sensitive_pos(signals); sensitive_neg(signals); | SC_CTHREAD( call_back, clock.pos()); SC_CTHREAD( call_back, clock.neg()); |

#### Process Example

#### Into the .H file

```

void doIt( void );

SC_CTOR( Mux21 ) {

SC_METHOD( doIt );

sensitive << selection;

sensitive << in1;

sensitive << in2;

}</pre>

```

#### Into the .CPP file

```

void Mux21::doIt( void ) {

sc_uint<8> out_tmp;

if( selection.read() ) {

out_tmp = in2.read();

} else {

out_tmp = in1.read();

}

out.write( out_tmp );

}

```

# **Ports and Signals**

- Ports of a module are the external interfaces that pass information to and from a module

- In SystemC one port can be IN, OUT or INOUT

- Signals are used to connect module ports allowing modules to communicate

- Very similar to ports and signals in VHDL

# **Ports and Signals**

- Types of ports and signals:

- All natives C/C++ types

- All SystemC types

- User defined types

- How to declare

- IN : sc\_in<port\_typ>

- OUT : sc\_out<port\_type>

- Bi-Directional : sc\_inout<port\_type>

# **Ports and Signals**

- How to read and write a port ?

- Methods read( ); and write( );

- Examples:

- in\_tmp = in.read( ); //reads the port in to in\_tmp

- out.write(out\_temp); //writes out\_temp in the out port

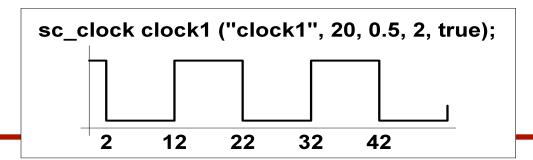

#### **Clocks**

- Special object

- How to create ?

sc\_clock clock\_name (

"clock\_label", period, duty\_ratio, offset, initial\_value);

- Clock connectionf1.clk( clk\_signal ); //where f1 is a

- Clock example:

#### Hello World!

```

// All systemc modules should include systemc.h header file

2 #include "systemc.h"

3 // Hello_world is module name

SC_MODULE (hello_world) {

SC_CTOR (hello_world) {

// Nothing in constructor

void say_hello() {

//Print "Hello World" to the console.

cout << "Hello World.\n";

10

11

12 };

13

14 // sc_main in top level function like in C++ main

int sc_main(int argc, char* argv[]) {

hello_world hello("HELLO");

16

// Print the hello world

17

18

hello.say_hello();

19

return(0);

20 }

```

#### counter

```

2 // This is my second Systemc Example

// If enable is active, then we increment the counter

28

3 // Design Name : first_counter

} else if (enable.read() == 1) {

29

4 // File Name : first_counter.cpp

count = count + 1;

30

5 // Function: This is a 4 bit up-counter with

31

counter out.write(count);

6 // Synchronous active high reset and

cout<<"@" << sc_time_stamp() <<" :: Incremented Counter "

32

// with active high enable signal

<<counter out.read()<<end|;

33

34

#include "systemc.h"

} // End of function incr count

35

10

36

11 SC MODULE (first counter) {

// Constructor for the counter

37

// Clock input of the design

sc in clk

clock ;

// Since this counter is a positive edge trigged one,

38

sc in<bool> reset ;

// active high, synchronous Reset input

13

// We trigger the below block with respect to positive

39

14

sc in<book> enable;

// Active high enable signal for counter

// edge of the clock and also when ever reset changes state

40

sc out<sc uint<4> > counter out; // 4 bit vector output of the counter

SC CTOR(first counter) {

41

16

cout<<"Executing new"<<endl;

42

//-----Local Variables Here-----

17

SC_METHOD(incr_count);

43

18

sc uint<4>

count:

44

sensitive << reset;

19

45

sensitive << clock.pos();

//-----Code Starts Here-----

20

// Below function implements actual counter logic

46

} // End of Constructor

21

22

void incr_count () {

48 }; // End of Module counter

23

// At every rising edge of clock we check if reset is active

24

// If active, we load the counter output with 4'b0000

25

if (reset.read() == 1) {

```

26

27

count = 0;

counter\_out.write(count);

### Final issues

- Come by my office hours (right after class)

- Any questions or concerns?