# Interfacing FPGAs with High Speed Memory Devices

#### **Agenda**

- Memory Requirements

- Memory System Bandwidth

- Do I Need External Memory?

- Altera<sup>®</sup> External Memory Interface Support

- Memory Interface Challenges

- Memory Interface Solutions

- DRAM

- Single Data Rate (SDR), Double Data Rate (DDR), DDRII

- FCRAM, RLDRAM

- SRAM

- Quad Data Rate (QDR)/QDRII SRAM

- Zero Bus Turnaround (ZBT)/NoBL SRAM

- Signal Timing & Board Design

#### **Memory Requirements**

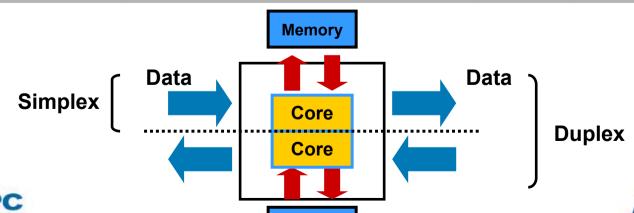

#### **Memory System Bandwidth**

| Data<br>Flow | Applications ( | Link Rate (Gbps)  Read/Write Memory Bandwidth (Gbps) |                        | Memory<br>Access           | Memory Banks Required   |                         |   |

|--------------|----------------|------------------------------------------------------|------------------------|----------------------------|-------------------------|-------------------------|---|

|              |                |                                                      | Overhead<br>40% (Gbps) | DDR<br>400<br>SDRAM<br>x72 | DDR 533<br>SDRAM<br>x72 | DDR 533<br>SDRAM<br>x72 |   |

| Simplex      | 1G Ethernet    | 1.25                                                 | 2.5                    | 3.5                        | 1                       | 1                       | 1 |

|              | 10G Ethernet   | 10                                                   | 20                     | 2.8                        | 2                       | 1                       | 1 |

|              | 40G Ethernet   | 40                                                   | 80                     | 112                        | 2                       | 1                       | 1 |

| Duplex       | 1G Ethernet    | 1.25                                                 | 5                      | 7                          | 1                       | 1                       | 1 |

|              | 10G Ethernet   | 10                                                   | 40                     | 56                         | 3                       | 2                       | 2 |

|              | 40G Ethernet   | 40                                                   | 160                    | 224                        | 9                       | 7                       | 7 |

**Memory**

#### **Do I Need External Memory?**

- Most FPGA Architectures Now Include On-Chip Blocks of SRAM

- Fine-Grain (< 1Kb) & Coarse-Grain (> 500Kb)

- Densities up to 10Mb

- 300+ MHz Performance without Off-Chip Latency

- Flexible Depth, Width, & Number

- Abundant Routing between Logic & Memory

- No off-Chip I/O Placement or Routing Issues

| Altera FPGA | Max. Memory Bits |

|-------------|------------------|

| Stratix™    | 10,118,016       |

| Stratix GX  | 3,423,744        |

| Cyclone™    | 294,912          |

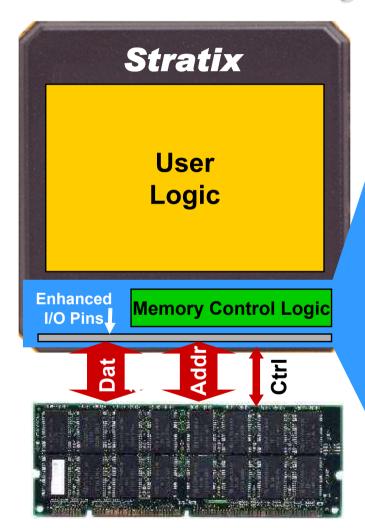

#### **FPGAs & External Memory**

- Interface to External Memory When Internal FPGA Memory Capacity is Insufficient

- FPGA Includes Enhanced I/O Circuitry to Maximize Data Access Performance

- Off-the-Shelf, Customizable Controllers

Minimize Development Time

| Memory Technology             | Clock Speed in FPGA | I/O Type         |

|-------------------------------|---------------------|------------------|

| SDR SDRAM (1)                 | 167 MHz             | LVTTL (3.3V)     |

| DDR SDRAM                     | 167 MHz             | SSTL-2 (2.5V)    |

| DDR Fast Cycle RAM (FCRAM)    | 200 MHz             | SSTL-2 (2.5V)    |

| Reduced Latency DRAM (RLDRAM) | 200 MHz             | HSTL (1.8V/1.5V) |

| QDR SRAM (2)                  | 167 MHz             | HSTL (1.5V)      |

| QDRII SRAM                    | 167 MHz             | HSTL (1.5V)      |

| ZBT (NoBL) SRAM (3)           | 200 MHz             | LVTTL (3.3V)     |

(3) Zero Bus Turnaround; No Bus Latency

<sup>(1)</sup> Synchronous Dynamic Random Access Memory

<sup>(2)</sup> Static Random Access Memory

#### **Altera Memory Controller IP**

**Memory Module or Device**

- Altera Memory Controller MegaCore<sup>®</sup> Functions

- Low-Cost, Drop-In Blocks of IP

- Hardware-Tested on Internal Test Platform

- Fully Supported

- Altera Megafunction Partner Program (AMPP) Functions

- Fully Customizable through Design Services

- Altera® Memory Controller Design Examples

- -Free, Open Source

### Memory Interface Solutions

#### **SDRAM Overview**

| Feature                     | Description                                                                    |

|-----------------------------|--------------------------------------------------------------------------------|

| Туре                        | SDR & DDR/DDRII SDRAM (Commodity)                                              |

|                             | FCRAM & RLDRAM (Low-Latency)                                                   |

| Clocking                    | All (Except SDR SDRAM) Require Clocking on Both<br>Edges of Differential Clock |

| Refresh                     | Requires Periodic Refresh Command to Maintain Contents                         |

| Bank<br>Management          | Memory Is Divided Into Multiple Banks that Require<br>Manual Opening & Closing |

| Initialization              | ■ Initialization Command Sequence Required on Power-Up                         |

| Data Strobe<br>(DQS) Signal | All (Except SDR SDRAM) Use a DQS Signal to Sample<br>Set of Data Signals       |

|                             | DDR SDRAM & FCRAM Use Bi-Directional DQS; RLDRAM Uses DQS for Reads Only       |

|                             | RLDRAM Uses Differential DQS                                                   |

#### **SDRAM Interfacing Requirements**

| Issue                                   | FPGA Solution                                                                                                                                                                                               |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Speed Operation (133/167/200+ MHz) | <ul> <li>Current Generation FPGA Supports 167+ MHz</li> <li>Core &amp; I/O Speeds</li> <li>Next Generation Supports 250+ MHz</li> </ul>                                                                     |

| DDR Data Generation                     | <ul> <li>Dedicated DDR Registers in I/O Element<br/>(IOE) Eliminate Need for Clock<br/>Doubling of High-Speed Internal Clocks</li> </ul>                                                                    |

| Data Strobe (DQS) Signal Alignment      | <ul> <li>Dedicated Strobe Signal Circuitry for Precise<br/>Alignment</li> <li>Phase Shifting Supports Data Window of Both<br/>DDR SDRAM &amp; FCRAM</li> </ul>                                              |

| Differential DQS<br>Signals (RLDRAM)    | <ul> <li>Use Dedicated I/O Circuitry for DQS &amp; Tie DQSn to VREF through Resistor</li> <li>Can Also Use Standard I/O Signals, Which Support Differential HSTL I/O &amp; Delay Signal on Board</li> </ul> |

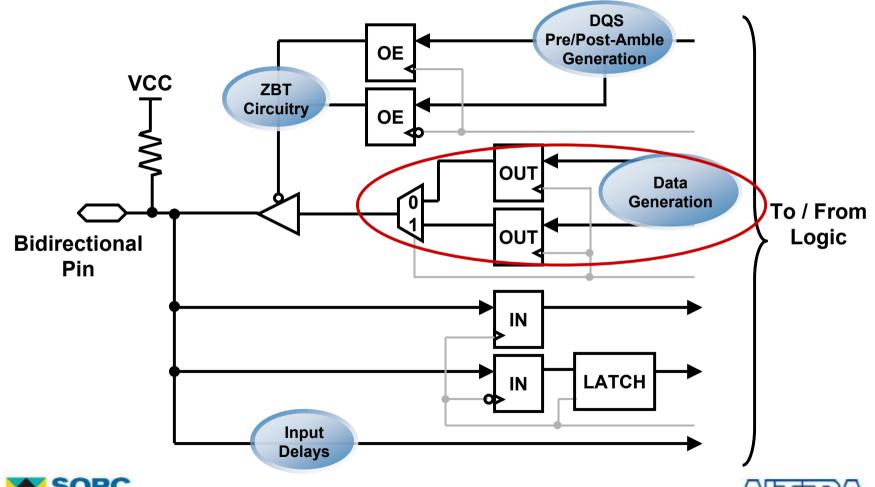

#### **DDR Support in I/O Element**

DDR Data Generation without Doubled Clock

ATTRA.

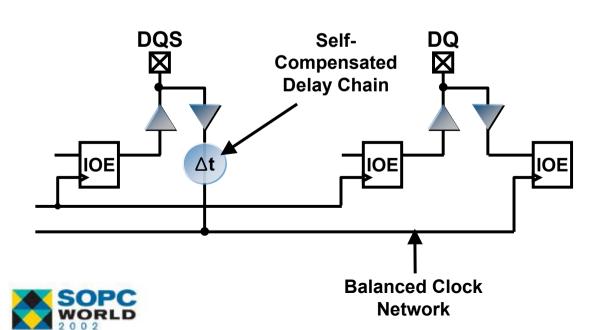

## Enhanced Data & Data Strobe Signal Interaction

- Optimized Data Strobe (DQS) Pins

- Self-Compensated Delay Chain Generates Shift on Data Read

- 90 Degrees for DDR SDRAM, 72 Degrees for FCRAM

- Drive Associated Data (DQ) Pins

- Uses Balanced, Local Clock Network

#### **SDRAM Requirements (Cont.)**

| Issue                                     | FPGA Solution                                                                                        |

|-------------------------------------------|------------------------------------------------------------------------------------------------------|

| Refresh, Initialization & Bank Management | Complex State Machine Logic Handled by<br>Drop-In IP Cores with SRAM-like Local<br>Interfaces        |

| I/O Standards                             | <ul> <li>Multiple I/O Standards Supported by I/O Elements</li> <li>Selectable by I/O Bank</li> </ul> |

| Difficulty of Board<br>Design             | <ul> <li>Board Design Guidelines Based on<br/>Hardware Proven Solutions</li> </ul>                   |

|                                           | On-Chip Termination in FPGA Removes<br>Need for Many External Resistors                              |

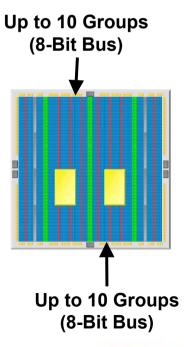

### SDRAM Interfaces in Altera FPGAs

| Interfaces                              | Stratix                         | Stratix GX                      | Cyclone                        |

|-----------------------------------------|---------------------------------|---------------------------------|--------------------------------|

| f <sub>MAX</sub> for SDRAM<br>I/F       | 167 MHz (200<br>MHz in –5)      | 167 MHz (200<br>MHz in –5)      | 133 MHz                        |

| Dedicated DDR<br>Registers              | Yes                             | Yes                             | No                             |

| Dedicated<br>Strobe Signal<br>Circuitry | Yes (Up to 160<br>Data Signals) | Yes (Up to 160<br>Data Signals) | Yes (Up to 40<br>Data Signals) |

| On-Chip<br>Termination                  | Yes                             | Yes                             | No                             |

#### **SDRAM Controller IP**

| Memory         | Device Support                  | Type                                         | Availability |

|----------------|---------------------------------|----------------------------------------------|--------------|

| SDR<br>SDRAM   | Stratix, Stratix<br>GX, Cyclone | Free Design<br>Example                       | Now          |

| DDR<br>SDRAM   | Stratix, Stratix<br>GX, Cyclone | MegaCore <sup>®</sup> & AMPP <sup>™</sup> IP | Now          |

| DDRII          | Next Generation                 | MegaCore IP                                  | 2003         |

| FCRAM<br>(DDR) | Stratix, Stratix GX             | MegaCore & AMPP IP                           | Now          |

| RLDRAM         | Stratix, Stratix GX             | MegaCore                                     | Q1 2003      |

### High-Performance SRAM Overview

| Feature       | Description                                                                                                                                                            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре          | <ul> <li>ZBT/NoBL for Higher Utilization of Shared Data Bus</li> <li>QDR/QDRII for High-Performance DDR Access on<br/>Dedicated Read &amp; Write Data Buses</li> </ul> |

| Clocking      | <ul> <li>Single-Edge for ZBT, Both Edges for QDR/QDRII</li> </ul>                                                                                                      |

| Control Logic | Much Simpler than SDRAM                                                                                                                                                |

### **SRAM Interfacing Requirements**

| Issue                                                  | FPGA Solution                                                                                                                                    |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Speed Operation (200 MHz)                         | <ul> <li>Current Generation FPGA Supports 200 MHz</li> <li>I/O and HSTL Signaling</li> <li>Next Generation Supports 300+ MHz</li> </ul>          |

| DDR Data Generation (QDR/QDRII)                        | Dedicated DDR Registers in I/O Element Allows<br>DDR Transfers without Requiring Clock<br>Doubling                                               |

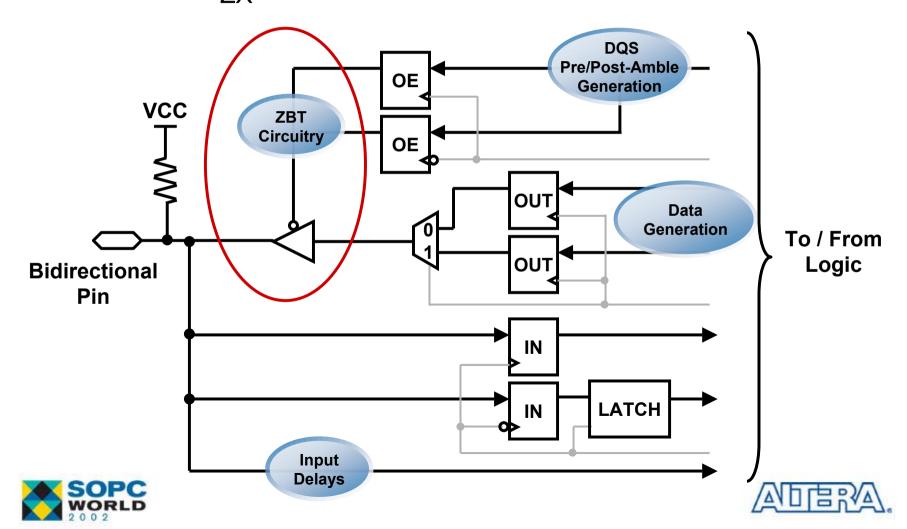

| Bus Contention<br>(ZBT/NoBL)                           | ■ Dedicated ZBT Circuitry for Increasing t <sub>ZX</sub> to Avoid Contention on Read-to-Write Transition                                         |

| Tight t <sub>co</sub> & t <sub>su</sub> Specifications | ■ Internal Phase-Locked Loops (PLLs) Enable Fast t <sub>CO</sub> & t <sub>SU</sub> Clock Shifting Feature Permits Accurate Data Capture on Reads |

| Clock Generation                                       | ■ PLL Generates Differential HSTL Clock for Memory Device                                                                                        |

#### **ZBT Support in I/O Element**

Increase t<sub>7x</sub> to Avoid Bus Contention

#### **SRAM Interfaces in Altera FPGAs**

| Interface                                | Stratix | Stratix GX |

|------------------------------------------|---------|------------|

| f <sub>MAX</sub> for SRAM Interface      | 200 MHz | 200 MHz    |

| Dedicated DDR Registers                  | Yes     | Yes        |

| Dedicated ZBT Circuitry                  | Yes     | Yes        |

| HSTL I/O Support (Class I & II)          | Yes     | Yes        |

| PLLs (for Clock Management & Generation) | 6-12    | 4-8        |

#### **SRAM Controller IP**

| Memory   | Device Support      | Type                   | Availability |

|----------|---------------------|------------------------|--------------|

| QDR      | Stratix, Stratix GX | Free Design<br>Example | Now          |

| QDRII    | Stratix, Stratix GX | Free Design<br>Example | Now          |

| ZBT/NoBL | Stratix, Stratix GX | Free Design<br>Example | Now          |

## Signal Timing & Board Design

#### **Board Timing Issues**

| Issue                                                            | FPGA Resolution                                                                                             |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Clock Generation                                                 | Use FPGA PLLs to Generate & Distribute Clocks for Greater Control & Simplified Routing                      |

| Clock Skew                                                       | Use External Feedback Mode of PLLs to Synchronize Source & Destination Clocks                               |

| t <sub>CO</sub> , t <sub>SU</sub> , t <sub>H</sub> Violations    | Use PLLs to Shift Clock Edges inside FPGA                                                                   |

| t <sub>ZX</sub> , t <sub>XZ</sub> Violations (Bus<br>Contention) | Use Dedicated ZBT Circuitry to Delay t <sub>zx</sub> of FPGA                                                |

| DQS Signal Alignment                                             | Match DQS & DQ Trace Lengths, Then Use Dedicated DQS Delay Circuitry to Provide Appropriate DQS Phase Shift |

Altera® Always Recommends Performing Board Timing Analysis for High-Speed Memory Interface Designs

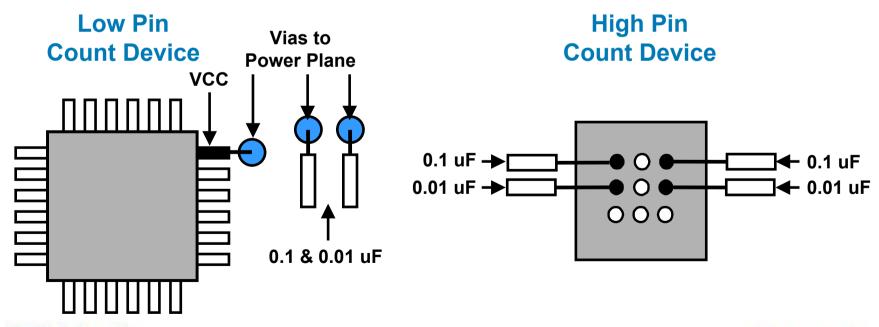

#### **Decoupling Guidelines**

- Improve Signal Integrity through Decoupling Capacitors

- Recommend Using 0.1 & 0.01 µF Capacitors per Power Pin on Low Pin Count Devices

- Faster Edge Rates (>100 MHz) May Require 0.001 μF As Well

- For High Pin Count Devices, Can Alternate between

0.1 μF & 0.01 μF on Adjacent Power Pins

- Hardware Tested on Altera® Internal Memory Test Board

- Larger Benefit than Placing Capacitors Farther from Pin

#### Other Board Design Guidelines

Ensure FPGA I/O Meets JEDEC Spec of 1v/ns with Class 1 & Class 2 Loads for Optimal Signal Integrity

Altera FPGAs are Compliant

Impedance & Termination

Match Lengths Where Possible

At a Minimum, Match Address/Control As One Group, Data As Another Match I/O Termination with Trace Impedance

Follow Memory Vendor's Guidelines

Use On-Chip Termination (Terminator<sup>TM</sup> Technology)

**External Termination**

**Terminator Technology**

#### **DIMM Design Guidelines**

- Dual In-line Memory Modules (DIMMs) Available For:

- SDR & DDR SDRAM

- RLDRAM

- Ensure FPGA Can Drive Large Capacitive Loads

- Altera FPGAs Can Drive Up to 25 pF

- Ensure FPGA Can Support 72-Bit Wide DDR I/O Per DIMM

- Stratix & Stratix GX Devices Can Support Two 72-Bit DIMMs with Dedicated DDR Circuitry

- Can Support Additional DIMMs, But May Require Lower Frequency or Careful Board Design

#### For More Information

- Visit http://www.altera.com

- Intellectual Property

- OpenCore® Evaluation Downloads for All Memory Controller IP

- Downloads for Memory Controller Free Design Examples

- Detailed Test Board Documentation Available on Request

#### Literature

- AN 212: Implementing Double Data Rate I/O Signaling in Stratix Devices

- AN 209: Using Terminator Technology in Stratix Devices

- AN 256: Implementing Double Data Rate I/O Signaling in Cyclone Devices