## SignalTap II

## **Agenda**

- SignalTap II Interface in Quartus II S/W

- SignalTap II Demonstration

- Initial Compilation

- Second Compilation:

Using SignalTap II Logic Analyzer

- Conclusions

# SignalTap II Interface in Quartus II Software

## SignalTap II File (.stp)

- Creating SignalTap® II Logic Analyzer File

- Choose New (File Menu)

- Click the Other Files Tab & Select SignalTap II File

- Click OK

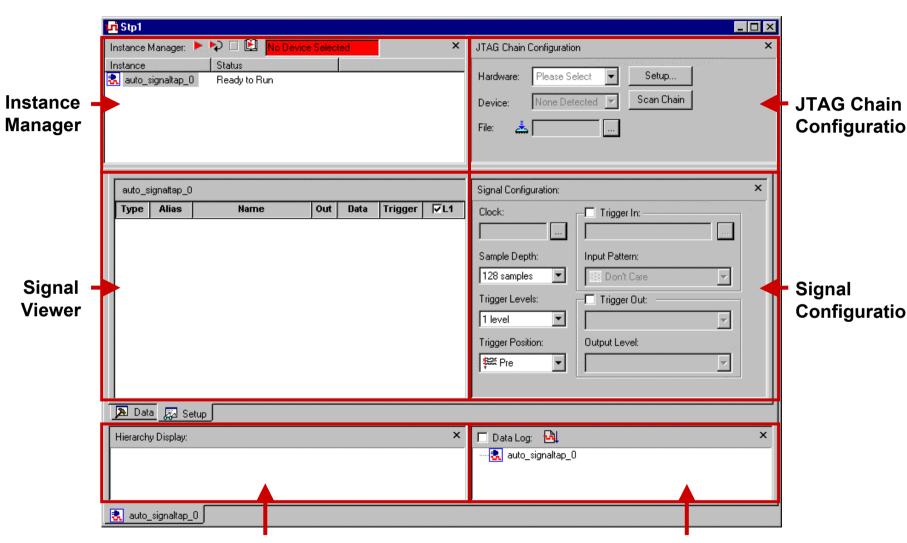

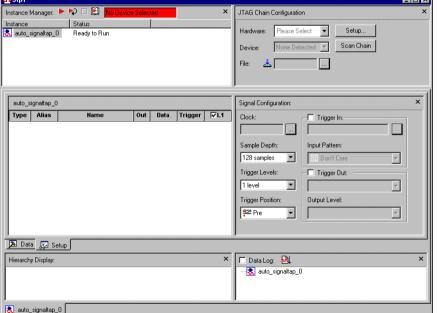

## SignalTap II File

## SignalTap II File: Acquisition Clock

#### Acquisition Clock

- For Best Results, Assign Only Global Clock as the SignalTap II Clock Signal

- Without Assigning Clock Signal, Quartus II Software Creates

Clock Pin auto stp external clock

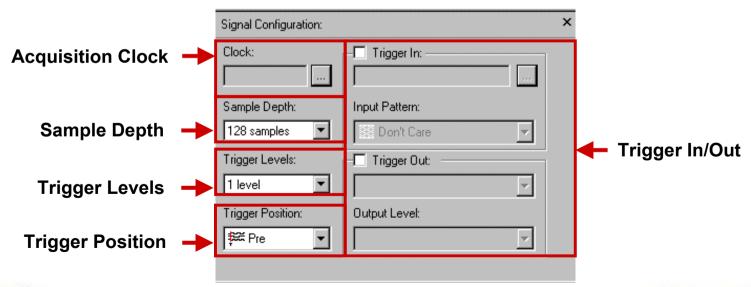

## SignalTap II File: Trigger Pattern

- Sample Depth

- Set Number of Samples Stored for Each Input Signal

- 0 to 128K Sample Depth

- Trigger Levels

- Configure Analyzer with up to 10 Trigger Levels

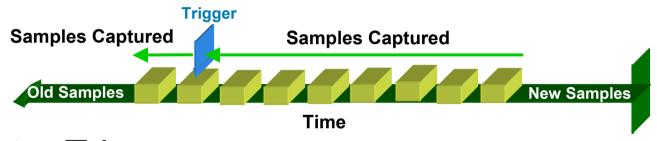

- Trigger Position

- Specify Amount of Data Captured by SignalTap II

Logic Analyzer that Should be Acquired before the

Trigger as well as Amount that Should be Acquired

after the Trigger

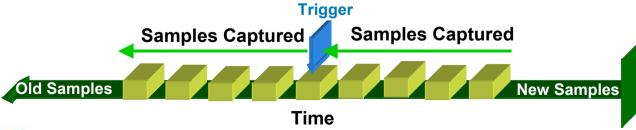

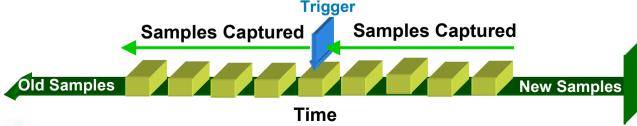

## **Trigger Position**

- Pre-Trigger

- Captures Signals that Occur Immediately after Triggering (12% Pre-Trigger, 88% Post-Trigger)

- Center Trigger

- Captures Signals before & after Triggering (50% Pre-Trigger, 50% Post-Trigger)

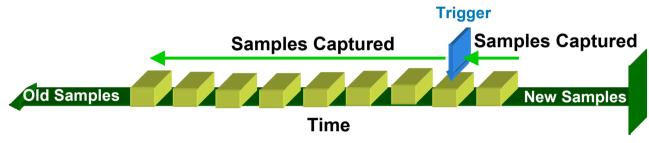

## **Trigger Position**

- Post-Trigger

- Captures Signal that Occur Immediately before Triggering (88% Pre-Trigger, 12% Post-Trigger)

- Continuous Trigger

- Captures Signals Indefinitely Until Stopped Manually (Useful When Using the Trigger Out Feature)

## SignalTap II File:Trigger In/Out

#### Trigger In

- Any I/O Pin Can Trigger the SignalTap II Analyzer

- Pin auto\_stp\_trigger\_in\_0 Generated in Device

- Trigger Input Can be Set to Recognize High, Low, Rising Edge, Falling Edge, Either Edge, or Don't Care Condition

#### Trigger Out

- Spare I/O Pin that Is Set as Trigger Output Signal That Indicates When Trigger Pattern Occurs

- Pin auto\_stp\_trigger\_out\_0 Generated in Device

- Output Pulse Polarity Is Programmable

## SignalTap II File: Debug Ports

- Routing SignalTap II Signal to Spare I/O Pin for Capture by Logic Analyzer

- Quartus II Software Automatically Generates a Pin

- Debug Port Pin Name Is stp\_debug\_out\_1\_n

- n Is a Number Representing the Order in Which the Debug Port Pin Occurs in the Signal List

| Туре       | Alias | Name           | Out              | Data          | Trigger | √L1 |

|------------|-------|----------------|------------------|---------------|---------|-----|

| <b>(3)</b> |       | CNT_ONE_ENABLE | -800             | V             | V       |     |

| <b>(B)</b> |       | CNT_ONE0       | -833             | V             | V       |     |

| <b>6</b>   |       | CNT_ONE1       | -                | Debug Port On |         |     |

| <b>(B)</b> |       | CNT_ONE2       | . Debug Port Off |               |         |     |

| <b>©</b>   |       | CNT_ONE3       | -800             | V             | V       |     |

# SignalTap II File: Control Settings

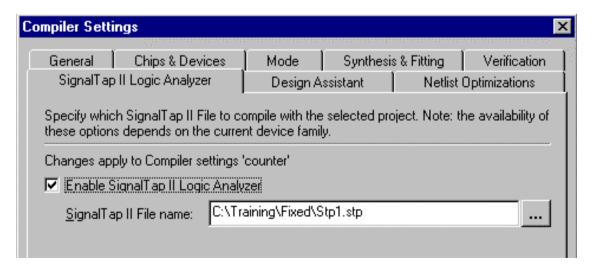

## **Specify SignalTap II File**

- Choose Compiler Settings (Processing Menu)

- Click the SignalTap II Logic Analyzer Tab

- Turn on Enable SignalTap II Logic Analyzer

- In the SignalTap II File Name box:

- Type the Name of the SignalTap II File (.stp) for Compilation

- Or Select a File Name with Browse Button

## **Project Compilation**

- Design Recompilation Required When Any of These Parameters Change

- Acquisition Clock

- Number of Channels

- Sample Depth

- Debug Ports

- Trigger in/out Ports

- Design Recompilation Not Required When

- Changing Trigger Pattern or Position

- Modifying Trigger Levels

- Starting or Stopping SignalTap II Logic Analyzer

- Internal Nodes to Be Analyzed Should be Inputs, Outputs, Register Outputs, or Memory Outputs

## SignalTap II Demonstration

- Description of the Test Case

- Initial Compilation

- Observing the Malfunction

- Second Compilation

- Creating the Embedded Logic Analyzer

- Debugging Design

- Third Compilation

- Fixing the Design Issue

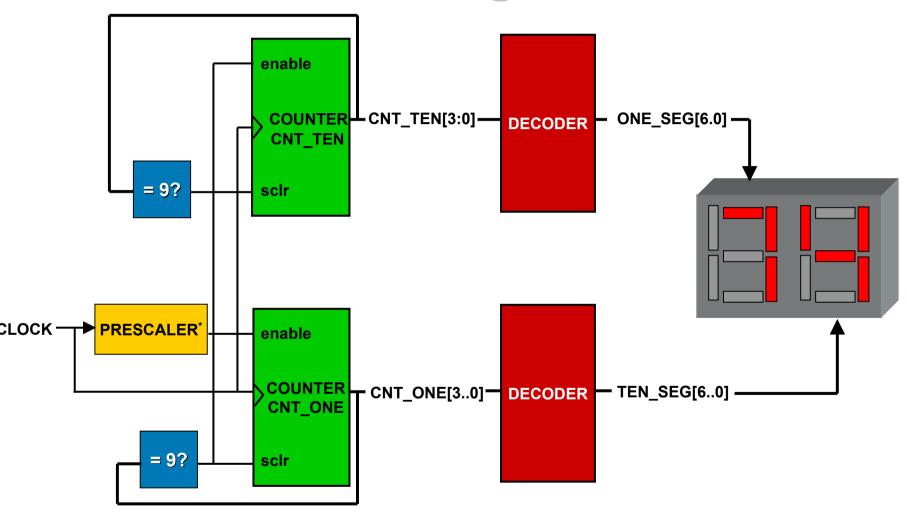

## Design: Counter from 00 to 99

- Function: Two 4-Bit Counters Cascaded to Drive a Pair of Seven-Segment LEDs that Count from 0 to 99

- Top Level Name: Counter

- Target Device : EP20K200EFC484-2X

- Tools

- Synthesis: LeonardoSpectrum

- Fitter: Quartus II Version. 2.1

- Place Source Design Files in C:\Training\Synthesis Directory

- Place pins.tcl File in C:\Training Directory

## **Counter Block Diagram**

\*: The Prescaler Generates a Counter Enable with a Frequency of about 1 Hz

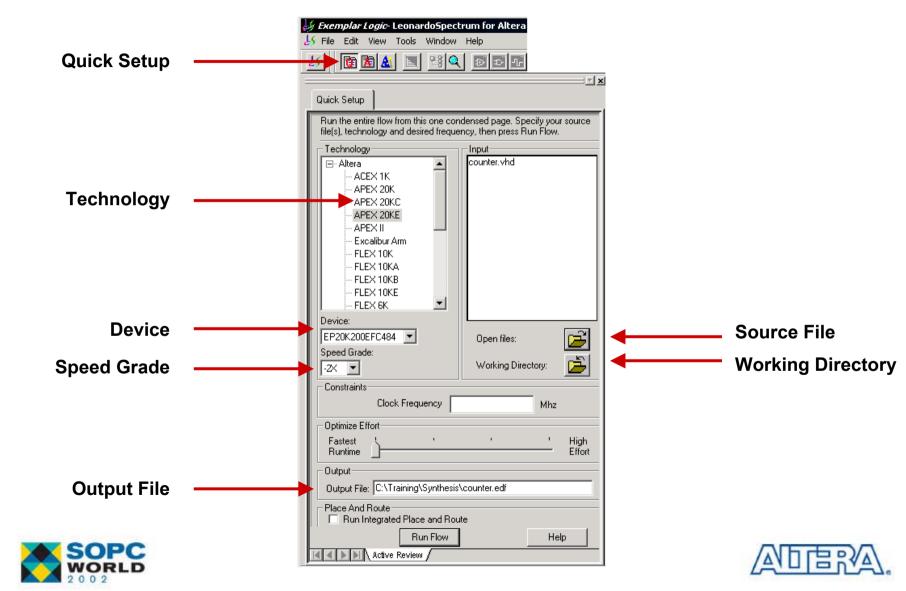

## Synthesize Design (1/2)

- Launch LeonardoSpectrum Tool

- Select Mode Quick Setup

Select Mode Quick Setup

Select Mode Quick Setup

Select Mode Quick Setup

- Working Directory: C:\Training\Synthesis

- Open Files: counter.vhd

- Technology: APEX 20KE

- Device: EP20K200EFC484

- Speed Grade: -2X

- Output File: C:\Training\Synthesis\counter.edf

- Click on Run Flow

## Synthesize Design (2/2)

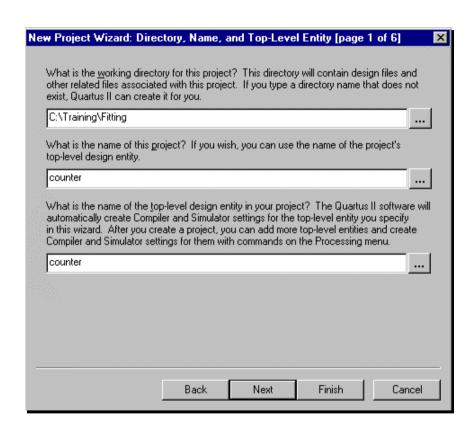

## **Create Quartus II Project**

- Launch the Quartus II Software

- Choose New Project

Wizard (File menu) to

Create a New Quartus II

Project

- Directory Name:C:\Training\Fitting

- Project Name: counter

- Top Level Name: counter

- Click Next

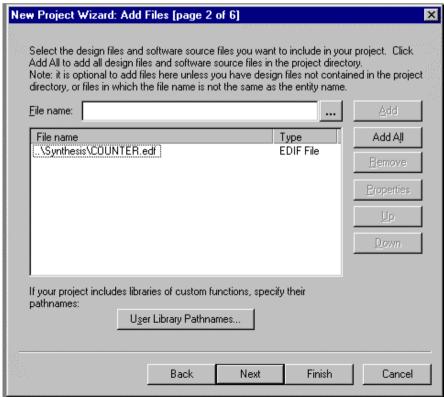

## **Create Quartus II Project**

- Add Following Files in Project

- C:\Training\Synthesis\counter.edf

- Click Next

- Click Finish

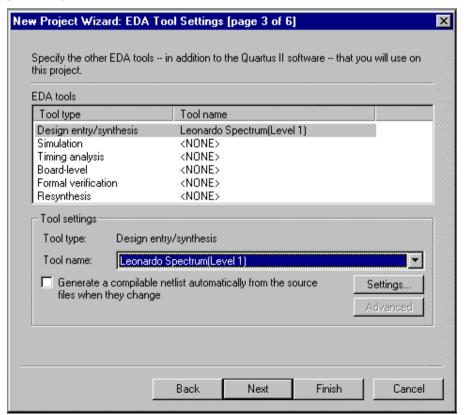

## **Create Project: Set EDA Tool**

- Select LeonardoSpectrum Tool (Level 1) as Design Entry/Synthesis Tool

- Click Next

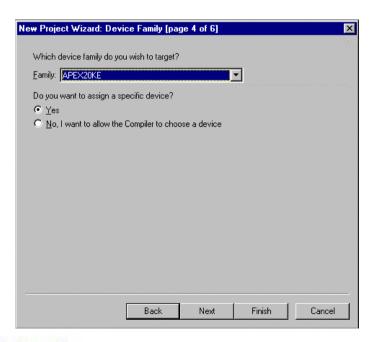

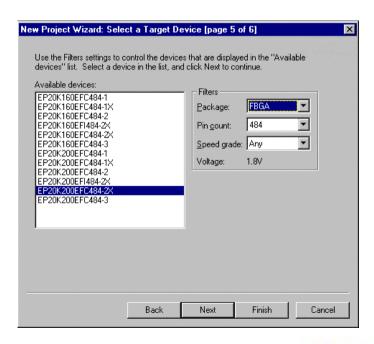

## **Create Project: Select Device**

- Select APEX & Yes to Assign Specific Device

- Click Next

- Select EP20K200EFC484-2X

- Click Finish

## Set All Unused I/Os as Tri-Stated

- Choose Compiler Settings (Processing Menu)

- Click the Chips & Devices Tab

- Click Device & Pin Options Button

- Click the Unused Pins Tab

- Select As inputs, tri-stated

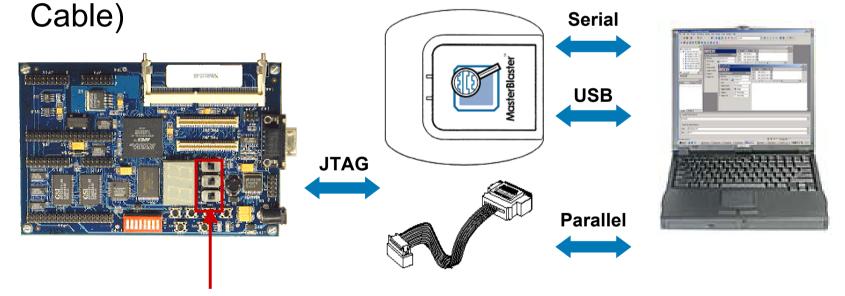

## **Hardware Setup**

- Nios Demo Board with APEX EP20K200EFC484-2X Device

- DC Power Supply

Device Download Cable (MasterBlaster or ByteBlasterMV

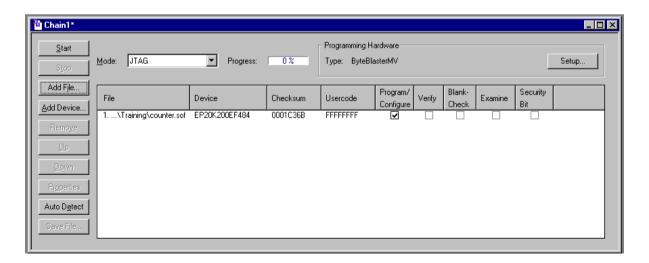

## **Compile Project & Configuration**

- Choose Start Compilation (Processing menu)

- Choose Open Programmer (Processing menu)

- Click Add File

- Select the File counter.sof

- Programming Hardware : ByteBlasterMV

- Mode : JTAG

- Check Option Program/Configure

- Click Start

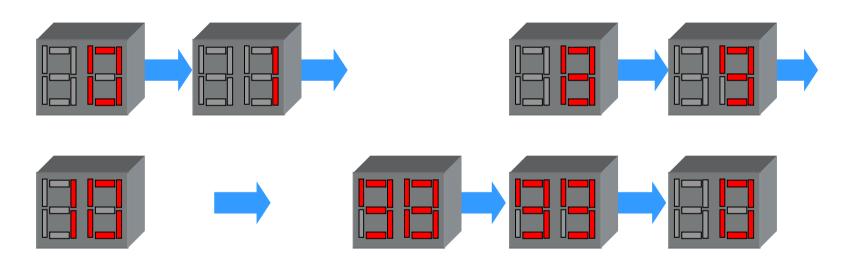

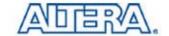

## **Observing the Malfunction**

Number 9 Never Appears on the Least & Most Significant Digit

SignalTap II Analyzer Used to Monitor Control Signals of LEDs

## **Essential Steps**

- Configure SignalTap II Logic Analyzer

- Select Nodes for Analysis

- Select Acquisition Clock

- Set Sample Depth & Trigger Options

- Enable the Logic Analyzer & Compile

- Configure Device

- Set the Trigger Pattern

- Run the SignalTap II Logic Analyzer

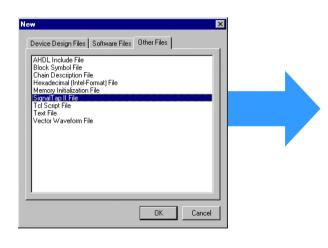

## **Configure Logic Analyzer**

- Choose New (File Menu)

- Click the Other Files Tab & Select SignalTap II File

Click OK

Or Select

Save the SignalTap II File as analysis.stp

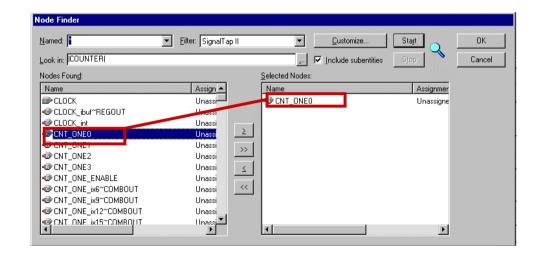

## **Analyzer 1: Select Nodes**

- Open Node Finder Window

- Double Click on the Signal Viewer

- Click Start to List All Pins & Internal Nodes

- Add Signal CNT\_ONE\_0 to Selected Nodes List

- Repeat

- CNT\_ONE\_1

- CNT\_ONE\_2

- CNT\_ONE\_3

- CNT\_ONE\_ENABLE

- Click OK

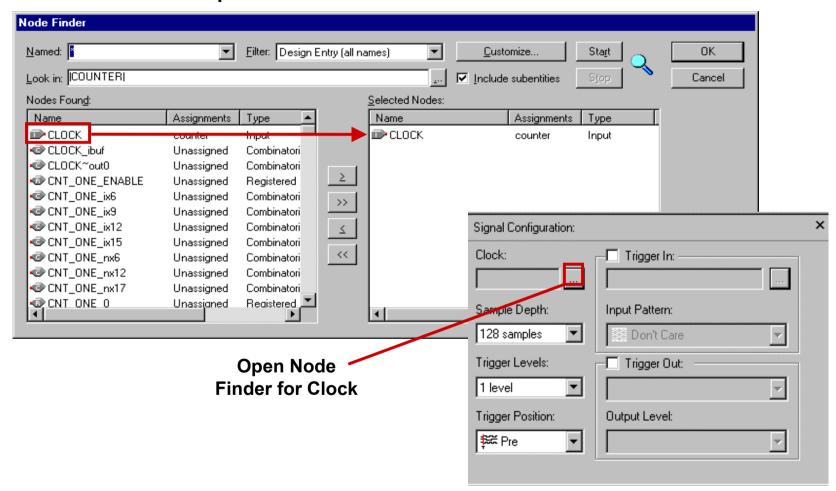

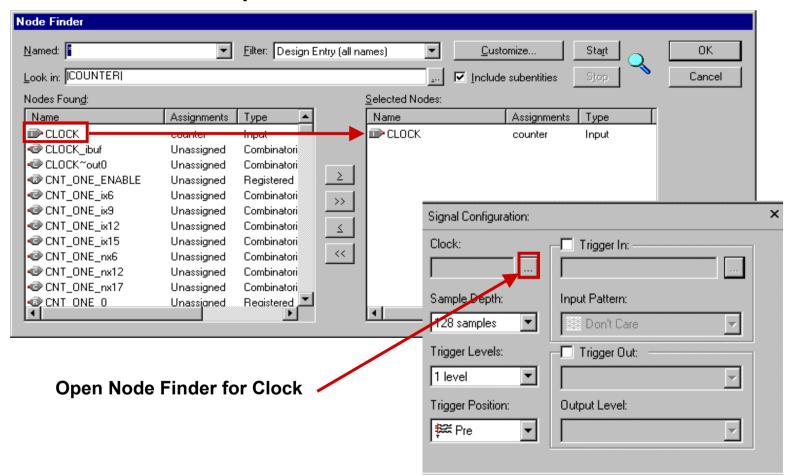

## **Analyzer 1: Acquisition Clock**

Add Clock Input Pin from Node Finder

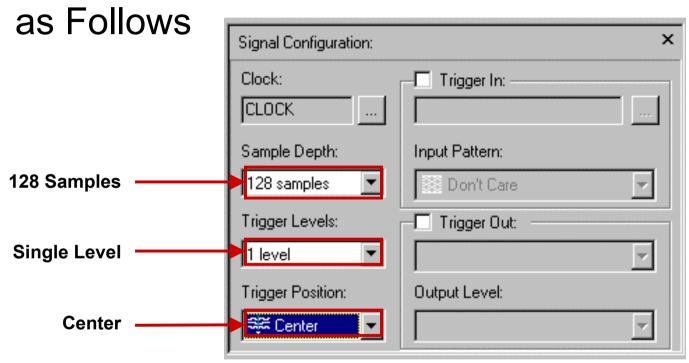

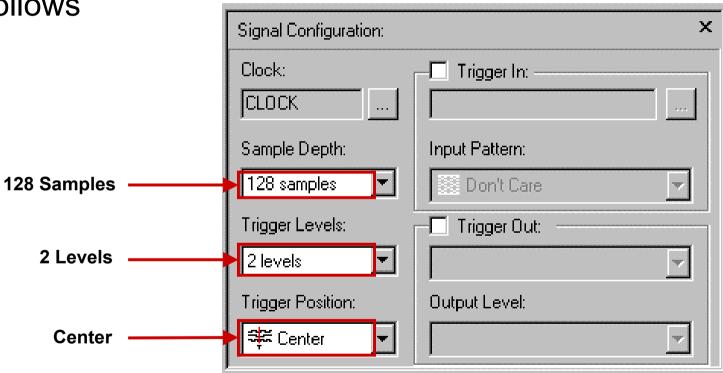

## **Configure Analyzer 1**

Configure Logic Analyzer 1 (auto\_signaltap\_0)

Choose Save (File menu)

## **Analyzer 2: Select Nodes**

- Right Click in Instance Manager & Select Create Instance

- Open the Node Finder Window

- Click Start to List All Pins & Internal Nodes

- Add Following Signals

- CNT\_ONE\_0, CNT\_ONE\_1, CNT\_ONE\_2, CNT\_ONE\_3

- CNT\_ONE\_ENABLE

- CNT\_TEN\_0, CNT\_TEN\_1, CNT\_TEN\_2, CNT\_TEN\_3

- Click OK

## **Analyzer 2: Acquisition Clock**

Add Clock Input Pin from Node Finder

## **Configure Analyzer 2**

Configure Logic Analyzer 2 (auto\_signaltap\_1) as

Follows

Choose Save (File menu)

# Compile Design with SignalTap II Logic Analyzer

- Choose Compiler Settings (Processing Menu)

- Click the SignalTap II Logic Analyzer Tab

- Turn on Enable SignalTap II Logic Analyzer

- Browse to analysis.stp File

- Click OK

- Choose Start Compilation

- (Processing menu)

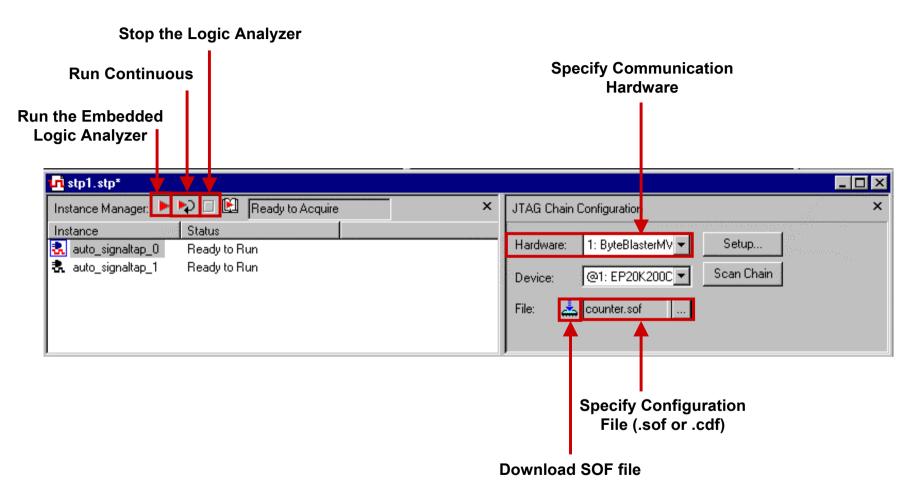

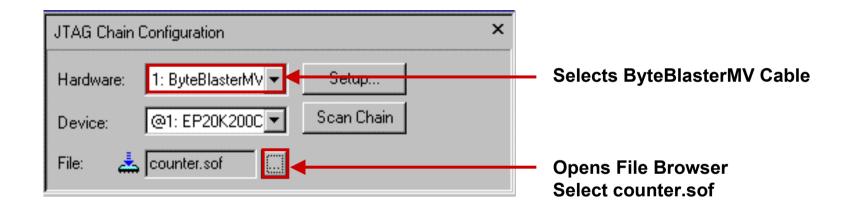

## **Running Analysis**

Select Hardware & Configuration File

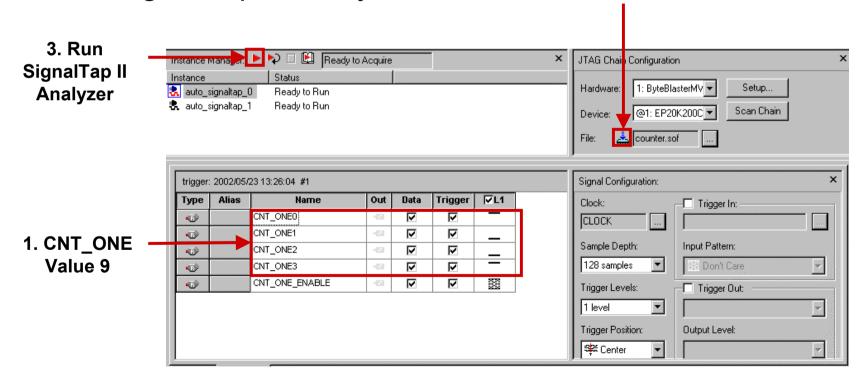

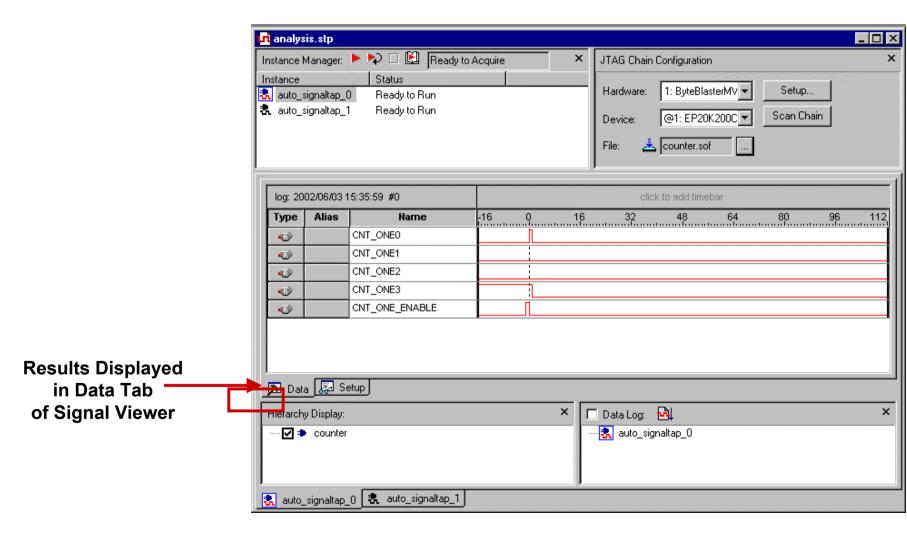

## Running Analyzer 1

- Set Trigger Pattern When CNT\_ONE Reaches 9

- Configure Device

- Run SignalTap II Analyzer

2. Configure Device

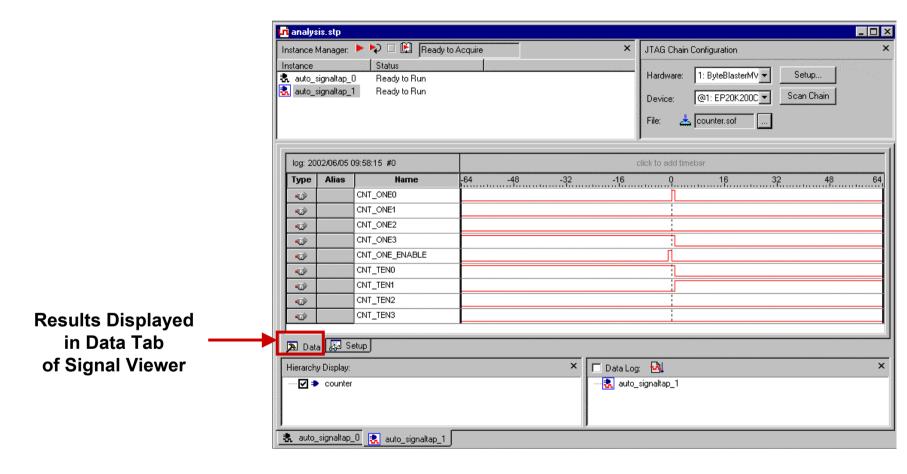

### **View Results**

## **Isolating the Problem**

The CNT\_ONE Counts to 9 but its Synchronous Reset Signal Occurs on the Next Clock Immediately Resetting the Counter to Zero

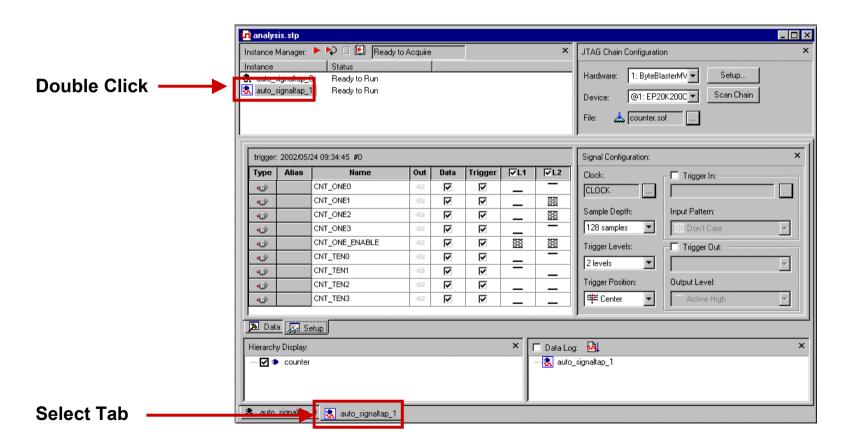

## **Analyzer 2 - Further Analysis**

Select Analyzer 2 - auto\_signaltap\_1

## Running Analyzer 2

- Set Trigger Pattern As Shown

- Configure Device

- Run SignalTap II Analyzer

Ready to Acquire JTAG Chain Configuration Status Instance Hardware 1: ByteBlasterMV ▼ Setup... auto\_signaltap\_0 Ready to Run 🚼 auto signaltap 1 Ready to Run @1: EP20K200C 🔻 Scan Chain 🚣 counter.sof trigger: 2002/05/24 09:34:45 #0 Signal Configuration: **⊽L1** Alias Name Out Data Trigger **VL2** Туре Clock: Trigger In: CNT\_ONE0 哮 CLOCK  $\overline{\mathbf{v}}$ ☑ CNT\_ONE1 Input Pattern: Sample Depth:  $\nabla$ CNT ONE2 哮 Ѿ  $\nabla$ 128 samples CNT ONE3 ☑ ☜ 굣  $\overline{\mathbf{v}}$ **\*\*** CNT ONE ENABLE **(** Trigger Out: Trigger Levels:  $\overline{\mathsf{v}}$ **(3)** CNT TENO  $\overline{\mathbf{v}}$ -2 levels CNT\_TEN1  $\overline{\mathsf{V}}$ **(3)** V Trigger Position: Output Level: CNT\_TEN2 ⊽ Ѿ ☑ **≋**≍ Center • CNT\_TEN3  $\nabla$ Y

Configure

**Device**

Run

SignalTap II

**Analyzer**

### **View Results**

#### **Conclusions**

## SignalTap II Benefits

- Access Internal Signals within Design

- Easy Configuration through Quartus II Interface

- Using SignalTap II Analyzer Does Not Require Making Modifications to Design Files

- Available with Quartus II Software