# PowerGauge with ModelSim

#### **Agenda**

- Power Estimation in Altera PLD

- PowerGauge<sup>™</sup> Power Analysis in Quartus<sup>®</sup> II Software

- Quartus<sup>™</sup> II Software/ ModelSim Overview

- Simulating with ModelSim

- Timing Simulation

- Calculate Power in Quartus II Software

# Power Estimation in Altera PLD

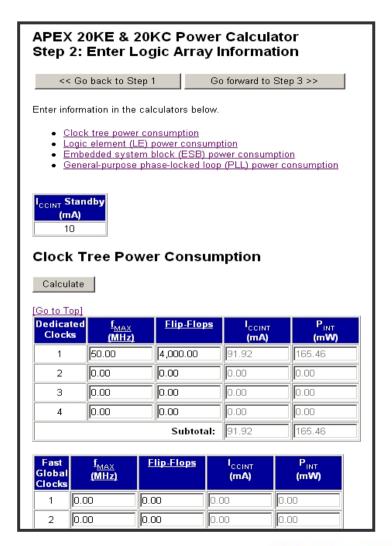

#### Web-Based Power Calculator

- Easy to Use with Click

- Need to Input Value from Report After Compilation In Quartus II

- Support APEX 20KE/C & APEX™ II & Mercury™ Devices (Supporting Stratix™ Devices Soon)

#### **Quartus II Power Calculator**

- 1. Must Make Vector

Wave Form File (\*.vwf)

for Using PowerGauge in

Quartus II Software

- 2. More Accurate than Web Based Power Calculator

- 3. Support APEX Family

& Mercury Devices

(Supporting Stratix

Devices in Next Version)

#### PowerGauge in Quartus II

#### PowerGauge Analysis Software

- Estimates Power Consumption Based on Toggle Rate

- Toggle Rate Derived from User Generated Simulation Vectors

- Use Quartus II Simulator

- Provides Support For Multiple I/O Standards

- Supports APEX 20KE & Mercury Families

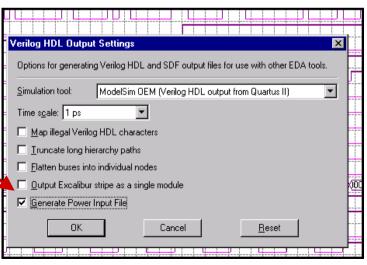

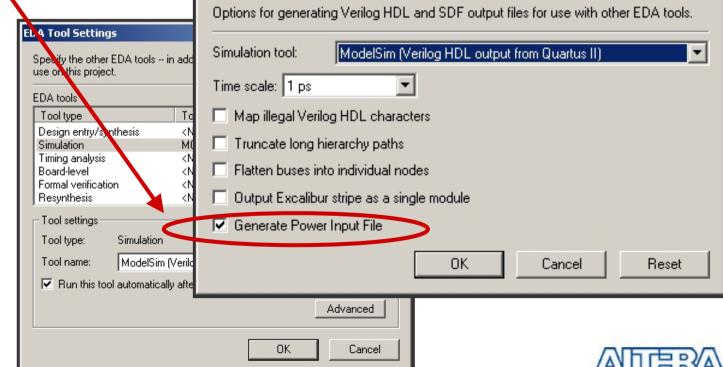

- Modelsim Can Output .Pwf File That Can Be Read by the Quartus II Simulator

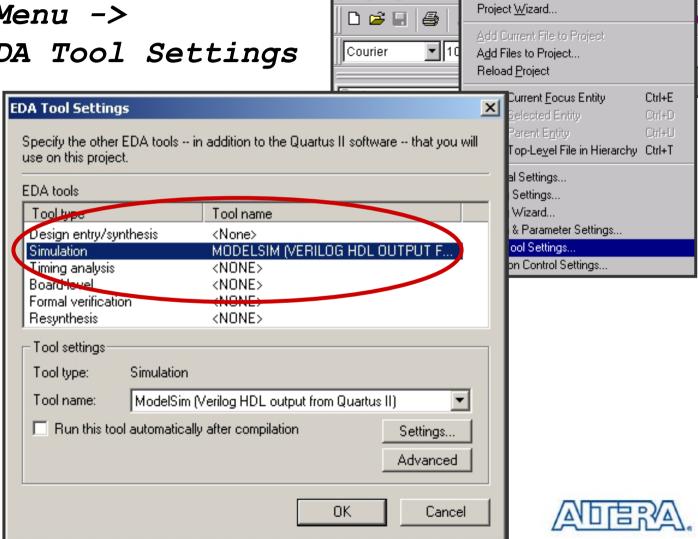

Project >EDA Tool Settings

>Modelsim Settings

Generate Power Input File

## Power Analysis in Quartus II

# Quartus II/ ModelSim Overview

#### **Basic Simulation Steps**

- 1 ⇒ Change Directory

- 2 ⇒ Create Library(s)

- **3** ⇒ Map Library to Physical Directory

- **4** ⇒ Compile Source Code

- All HDL Code Must Be Compiled

- Different for Verilog & VHDL

- **5** ⇒ Load Design

- 6 ⇒ Start Simulator

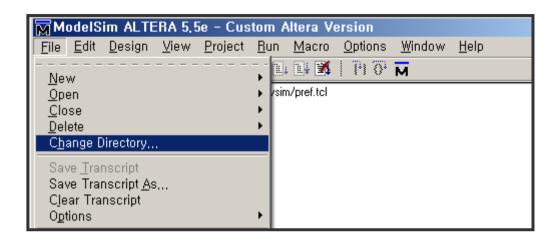

#### 1 ⇒ Change Directory

- UI) From within Main Window:

File -> Change Directory

- Cmd) From within Main, transcript window:

ModelSim> cd <drive>:/<directory name>

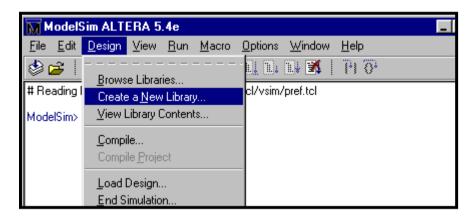

# 2 ⇒ Creating ModelSim Library(s)

UI) From within Main Window:

Design -> Create a New Library

Cmd) from within Main, transcript window:

ModelSim> vlib < library name>

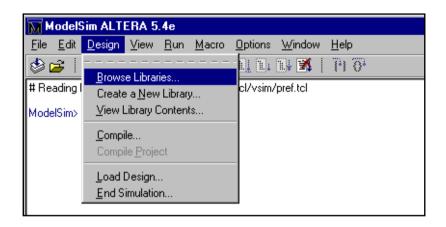

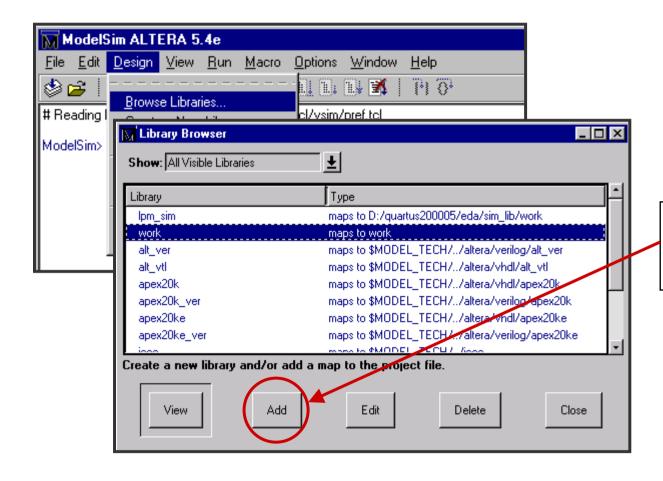

#### 3 ⇒ Map Logical Library Name(s)

Syntax: vmap <logical\_name> <directory\_path>

UI) From within Main Window:

Design -> Browse Libraries

Design -> Create a New Library

Cmd) From within Main, Transcript Window:

ModelSim> vmap my\_work c:\my\_design\my\_lib

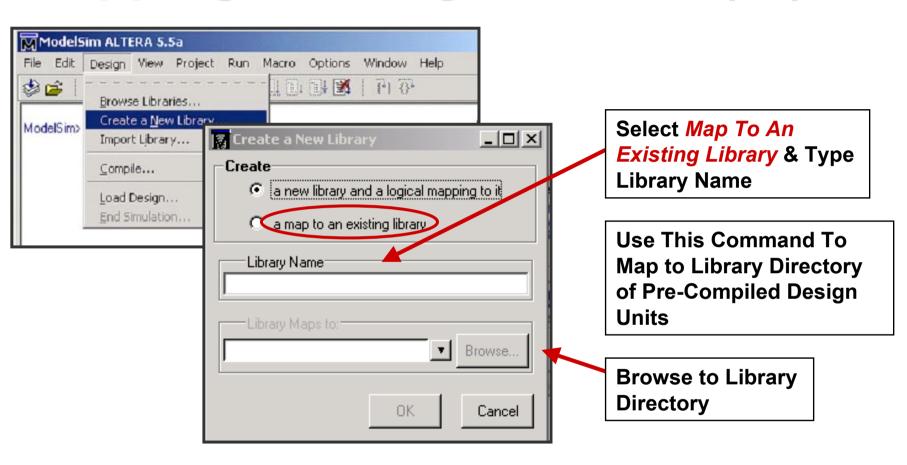

## **Mapping Existing Libraries (UI)**

-> vmap lpm\_sim c:\QuartusII\library\lpm

## **Mapping Existing Libraries (UI)**

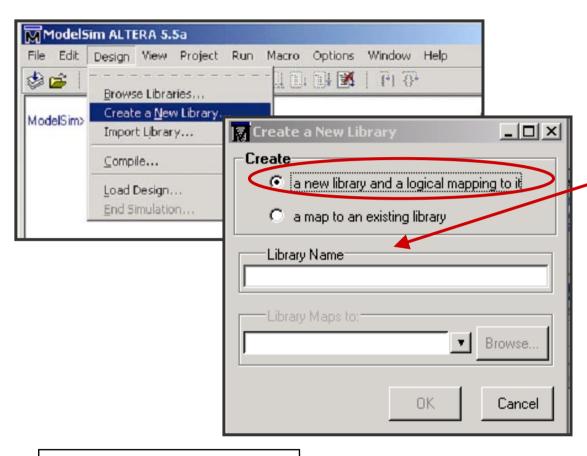

Select A New Library & A Logical Mapping to It & Type Library Name

This Command Creates Library Subdirectory in Local Directory & Then Sets Mapping for It

- -> vlib my\_lib

- -> vmap my\_lib my\_lib

## **Mapping Libraries (UI)**

Use Add Button to Create New Library & Map

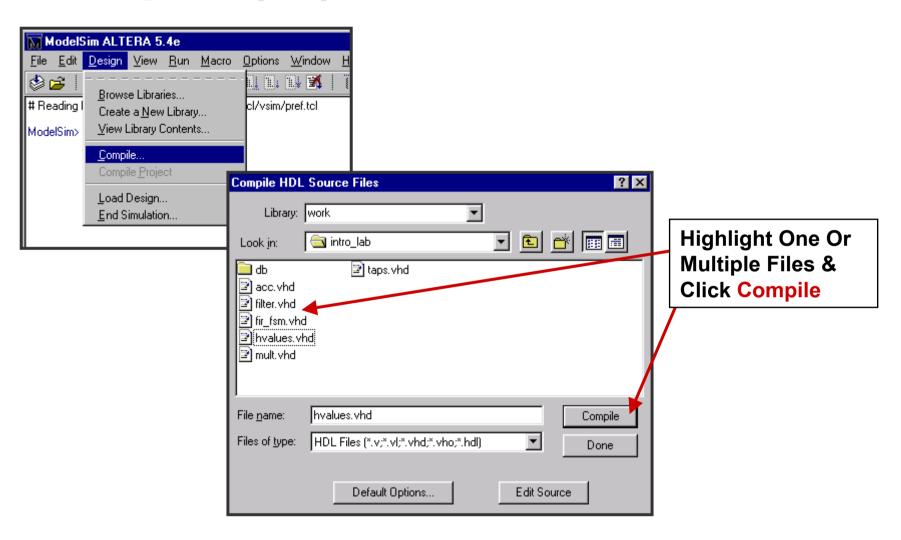

#### 4 ⇒ Compile Source Code (VHDL)

- UI) Design -> Compile

- Cmd) vcom -work <library\_name> <file1>.vhd <file2>.vhd

- Files Are Compiled in Order They Appear

- Compilation Order/Dependencies (Next Slide)

- '87 VHDL is default

- UI) Use Default Options button to set '93

- Cmd) Use -93 Option (Must Be First Argument)

- Default Compiles into Library Work

- Ex. Vcom -93 my\_design.vhd

Note: Design Units Must Be Re-Analyzed When Design Units They Reference Are Changed in Library.

# 4 Compile Source Code (Verilog)

- UI) Design -> Compile

- Cmd) vlog -work <library\_name> <file1>.v <file2>.v

- Files Are Compiled In Order They Appear

- Order Of Files or Compilation Does Not Matter

- Supports Incremental Compilation

- Default Compiles Into Library Work

- Ex. vlog my\_design.v

Note: Design Units Must Be Re-Analyzed When Design Units They Reference Are Changed in Library.

## Compile (UI)

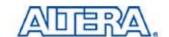

#### 5 ⇒ Load Design

- UI) Design -> Load New Design

- COM) vsim <top\_level\_design\_unit>

- VHDL

- vsim top\_entity top\_architecture

- Simulates Entity/Architecture Pair

- Can Also Choose A Configuration

- Verilog

- vsim top\_level1 top\_level2

- Simulates Multiple Top Level Modules

## Load Design (UI)

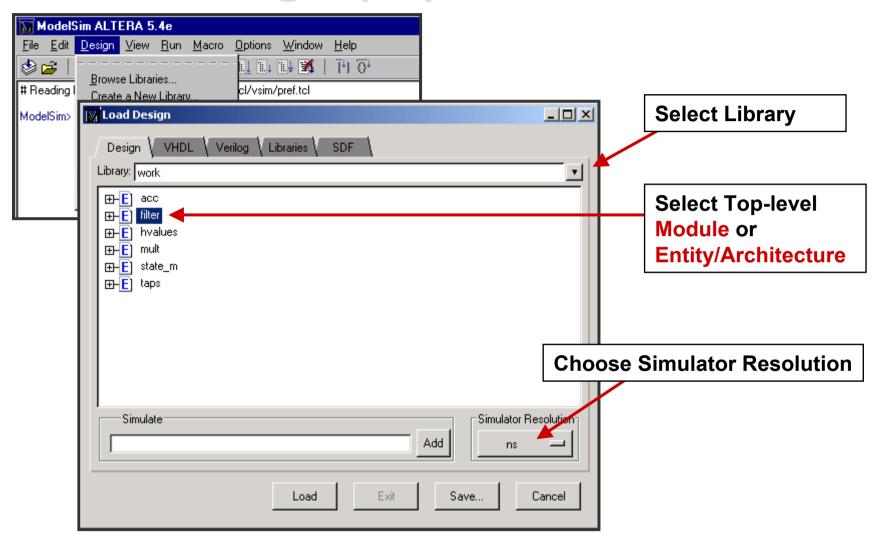

#### 6 ⇒ Start Simulator

- UI) Run

- COM) run <time\_step> <time\_units>

- Advances Simulator Amount of Timesteps Specified

## **Start Simulator (UI)**

Choose Number of Timesteps to Advance Simulator

Restart - Reloads Any

Design Elements that

Have Been Edited &

Resets Simulation Time to

Zero

COM) restart

# SOPC WORLD 2 0 0 2

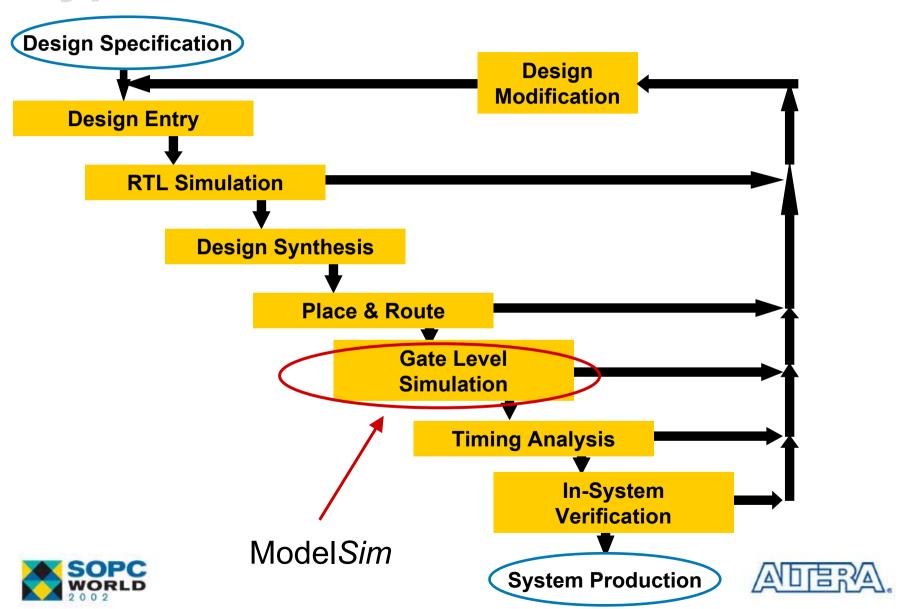

# Simulating with Model Sim Timing Simulation

## **Typical PLD Flow**

#### **Timing Simulation Files**

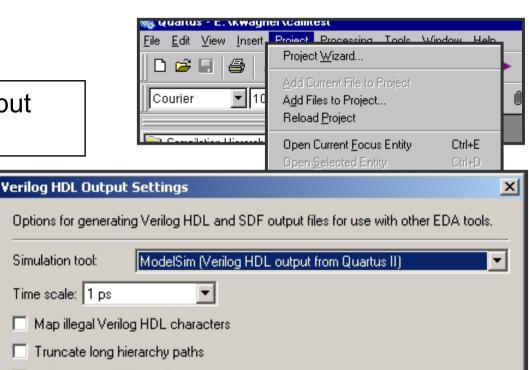

- Compile Design in Quartus II to Produce Output Files

- Output Simulation Files from Quartus II

- VO Verilog Output File (ATOM)

- VHO VHDL Output File (ATOM)

- SDO Standard Delay Format (SDF) Output File

- Annotates the delay for the elements in the output files

#### **Performing Timing Simulation**

- 1) EDA Tool Settings to Model Sim Verilog or VHDL

- 2) Compile Design In Quartus II to Produce Output Files

- 3) Create Testbench / Stimulus

- Can Use Stimulus from RTL Simulation

- 4) Perform Basic Simulation Steps

- Compile Quartus II Output File

- Map To ATOM Libraries

- Include SDO (Output SDF File) When Loading Design

#### **Before Compilation**

Project Menu -> EDA Tool Settings

R Guartus - C. Newaurier (Califices)

Edit View Insert Project Processing Tools Window Help

#### **NativeLink**

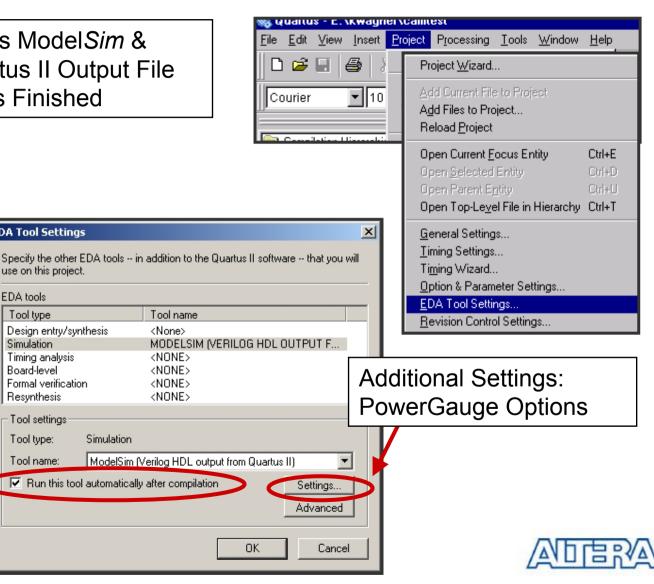

Automatically Starts Model Sim & Compiles the Quartus II Output File after Compilation Is Finished

EDA Tool Settings

use on this project.

Design entry/synthesis

Tool name

<None>

<NONE>

<NONE>

<NONE>

<NONE>

Simulation.

Run this tool automatically after compilation

EDA tools

Tool type

Simulation Timing analysis

Board-level

Resynthesis

Tool type: Tool name:

Tool settings

Formal verification

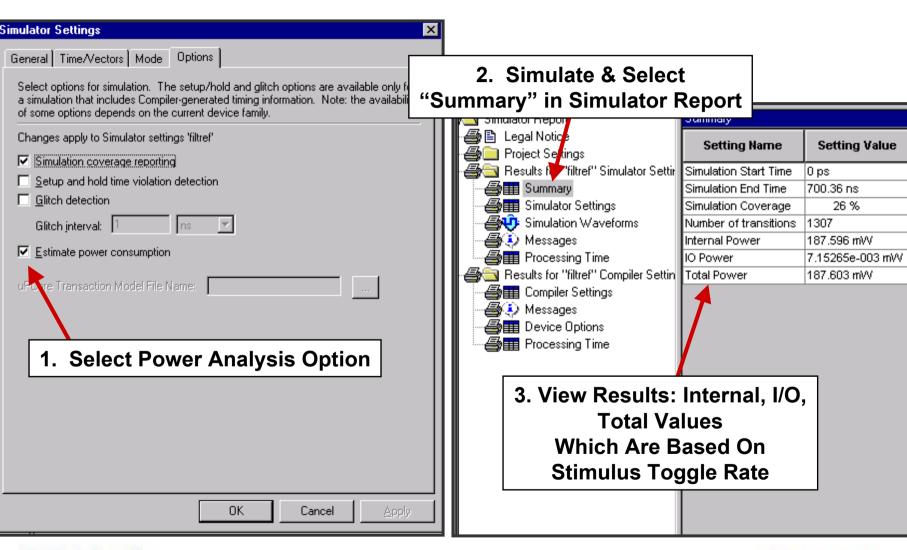

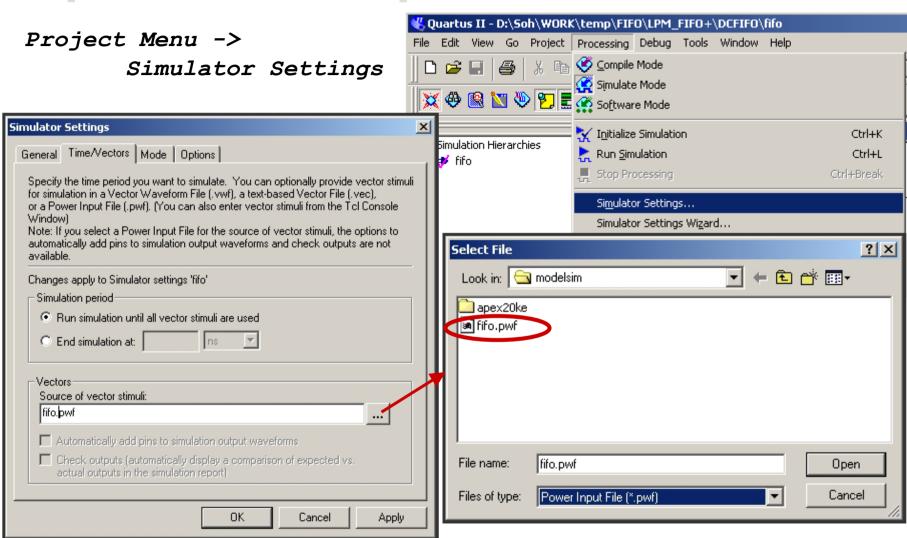

#### PowerGauge Options for ModelSim

Turn on Generate Power Input File (\*.pwr) option

#### **Libraries for Timing Simulation**

- ModelSim Altera OEM

- Must use Pre-compiled libraries

Modeltech\_ae\altera\vhdl

- ModelSim SE/PE

- ATOM libraries were located at Quartus\eda\sim\_lib

- Ex) For APEX20KE

Verilog: apex20ke\_atoms.v

VHDL: apex20ke\_atoms.vhd &

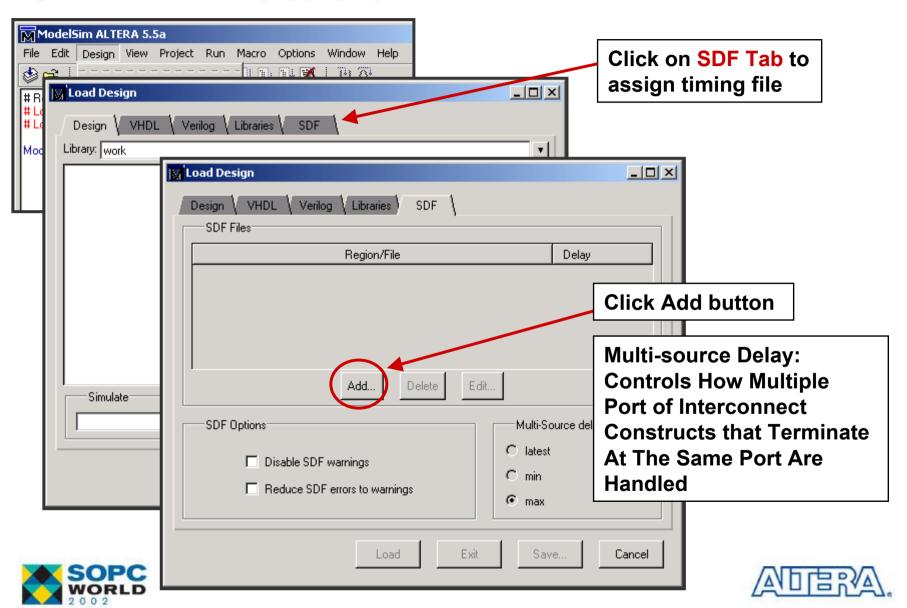

#### **SDF Annotation**

# Calculate Power in Quartus II

## **Open Power Input File**

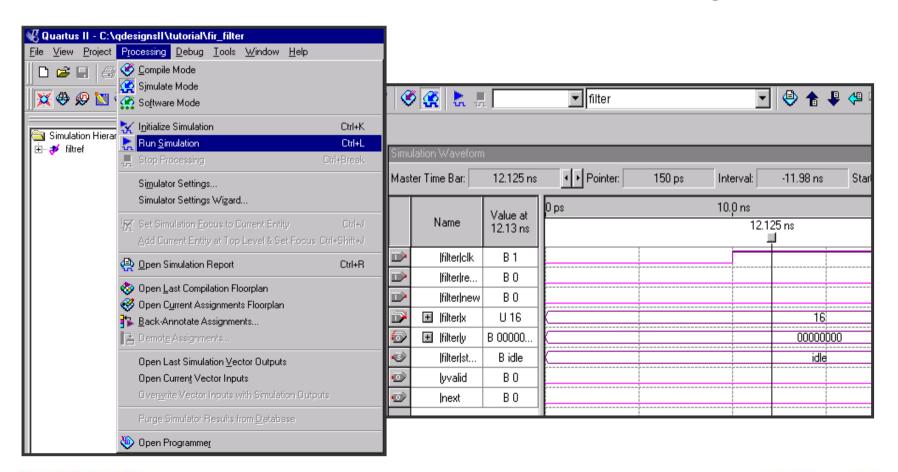

#### Running Simulation with PWF

Select Run Simulation from Processing Menu

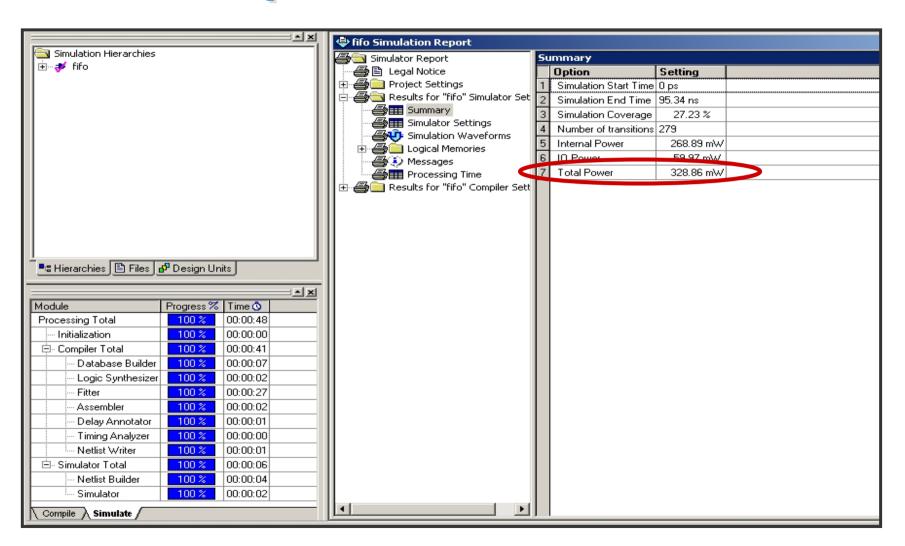

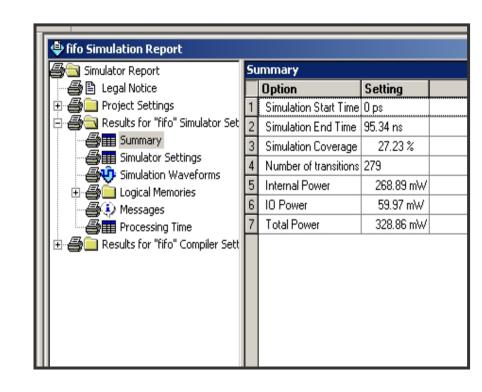

#### **Power Report in Quartus II**