20 YEARS of

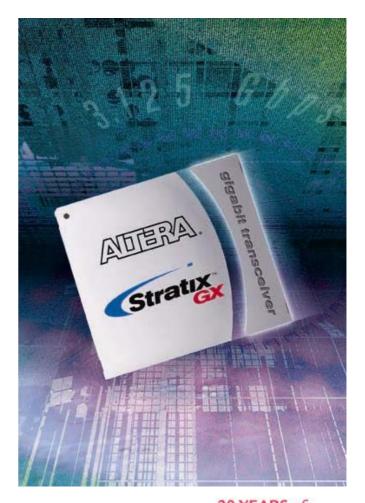

#### StratixGX Design Guideline

# The Low-Risk Path to 3.125-Gbps Transceiver Applications

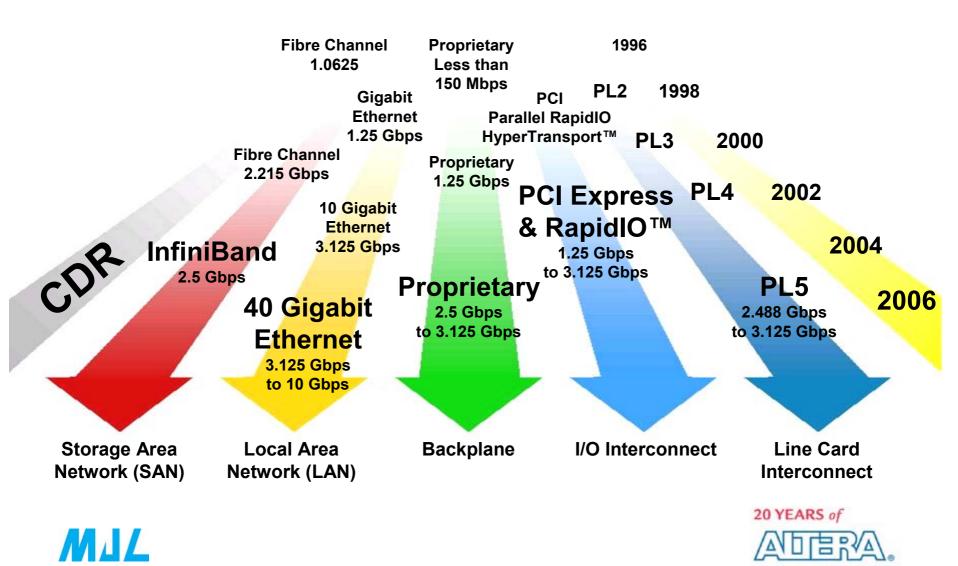

#### **Bandwidth Demand**

INNOVATION

# **Benefits of Transceiver Integration**

Easy Interface Protocol Bridging

Reduced Power Consumption

Eliminated Interoperability Issues

Simplified PCB Design & Real Estate Savings

Integration Reduces Time-to-Market & Lowers System Cost

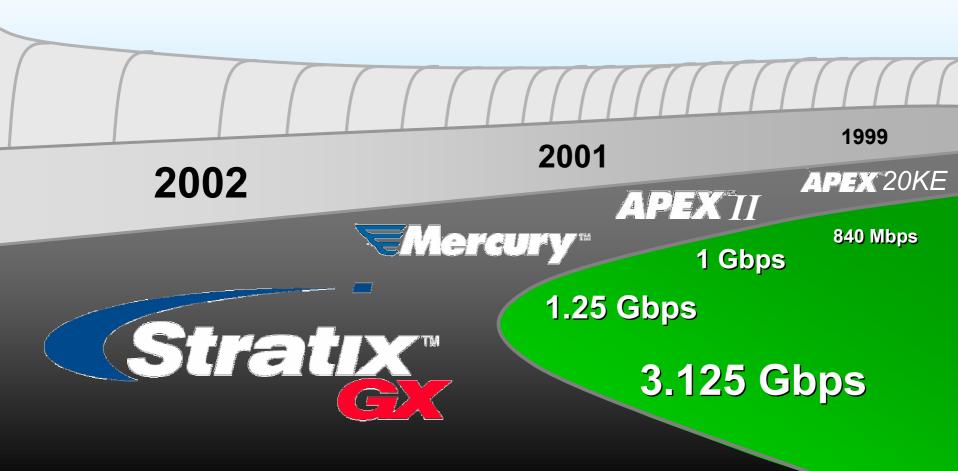

# **Building on Experience**

Industry Leadership in High-Speed I/O Innovation & Expertise

#### **Experience Drives Success**

Drive Capabilities

Suitable for Data

Transmission across

Backplanes

Optimized Logic-to-Transceiver Channel Ratio & Channel Configuration

Minimized Power

Consumption in Both

Transceiver & FPGA

Complete Soft IP

Portfolio for HigherLayer Function

Implementation

Balanced Data

Throughput on

Transceiver & SourceSynchronous Side

Implementation of Resource-Intensive Functions in Hard IP

Customer End-Product

Delivery Is the Goal

#### **Stratix GX Device Family**

| Device    | Logic<br>Elements | Full-Duplex<br>Transceiver<br>Channels | Source-<br>Synchronous<br>Channels with DPA | Total<br>Memory<br>Bits | DSP<br>Blocks |

|-----------|-------------------|----------------------------------------|---------------------------------------------|-------------------------|---------------|

| EP1SGX10C | 10,570            | 4                                      | 22                                          | 920,448                 | 6             |

| EP1SGX10D | 10,570            | 8                                      | 22                                          | 920,448                 | 6             |

| EP1SGX25C | 25,660            | 4                                      | 39                                          | 1,944,576               | 10            |

| EP1SGX25D | 25,660            | 8                                      | 39                                          | 1,944,576               | 10            |

| EP1SGX25F | 25,660            | 16                                     | 39                                          | 1,944,576               | 10            |

| EP1SGX40D | 41,250            | 8                                      | 45                                          | 3,423,744               | 14            |

| EP1SGX40G | 41,250            | 20                                     | 45                                          | 3,423,744               | 14            |

Supported in Quartus<sup>®</sup> II Software Version 2.1 Today

#### **Building on Stratix Architecture**

Stratix (străt'ĭks) n. The industry's fastest FPGA device family offering unrivaled logic & memory resources

(trăn-se' vər) n. Clock data recovery-based data transmission

**Transceiver**

technology supporting rates up to 3.125 Gbps

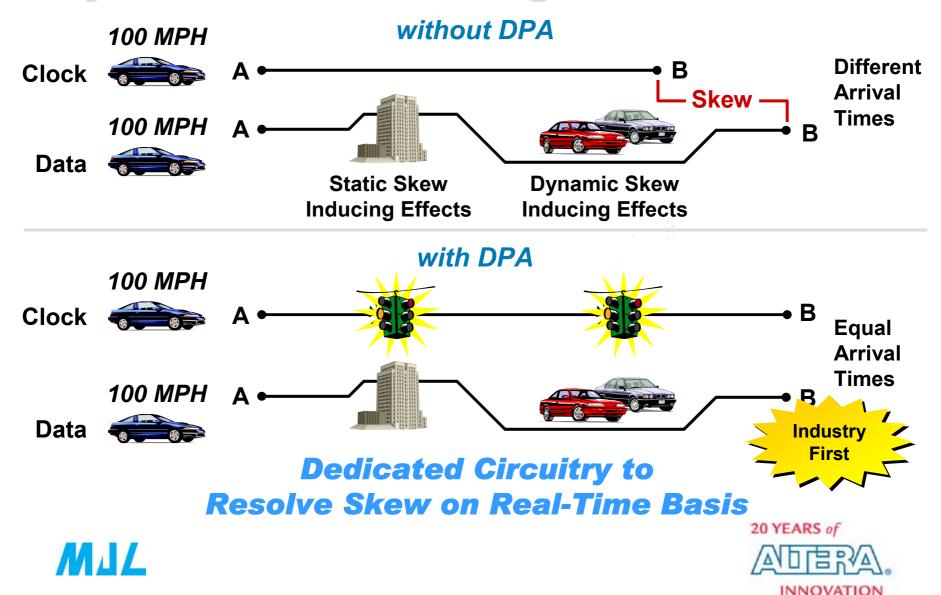

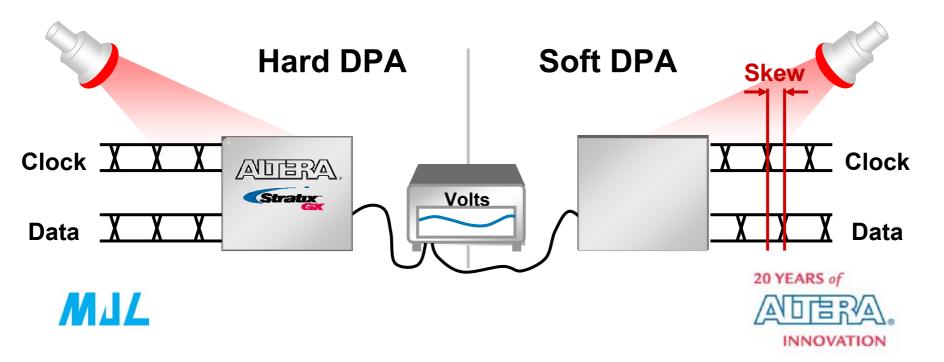

DPA (dē'pē ā) n. (dynamic phase alignment) Dedicated circuitry for resolving clock-to-channel and channel-to-channel skew, only found in Stratix GX devices

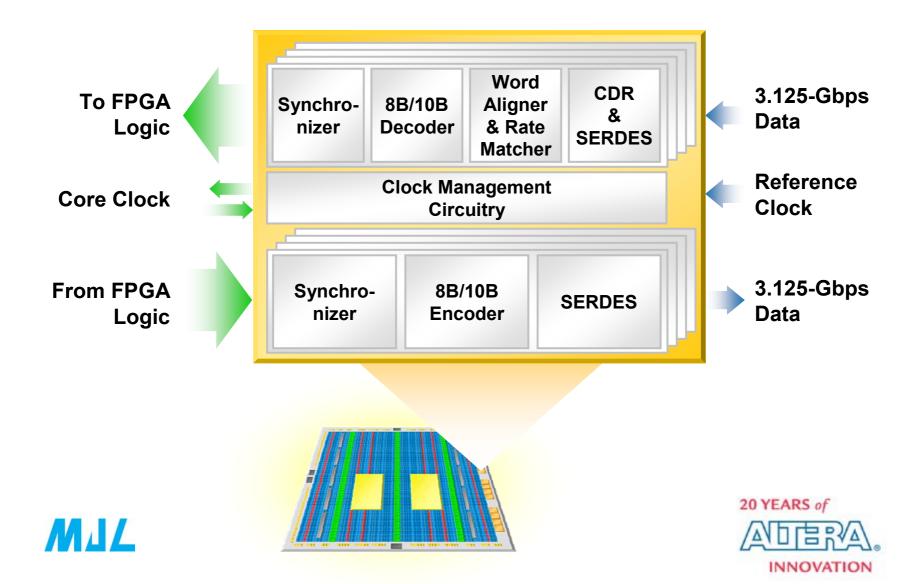

# Gigabit Transceiver Block

## **Dynamic Phase Alignment**

#### **Hard DPA Advantages**

- Ease of Implementation

- Simplifies Complex Clock Management

- Conserves General-Purpose Resources

- Logic, Global Clocks & PLLs

- Adjusts to Temperature & Voltage Changes

# Stratix GX Applications Overview

#### Backplane Interfaces

Traffic Management & QoS

Backplane & Switch Fabric Transceiver

## Chip-to-Chip Interfaces

- 10G Ethernet XAUI to XGMII Interface

- 10G Ethernet XAUI to POS-PHY 4 Bridge

- POS-PHY 4 to NPSI Bridge

- NPSI to Backplane Bridge

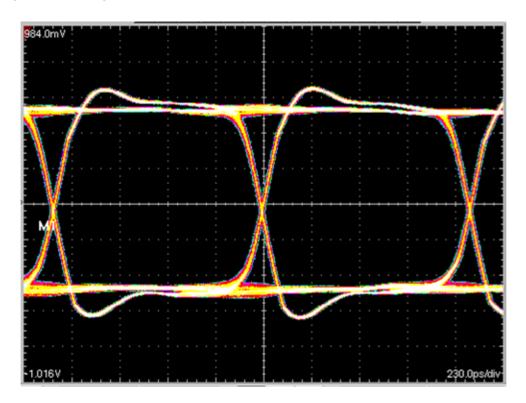

# Working 3.125-Gbps Silicon

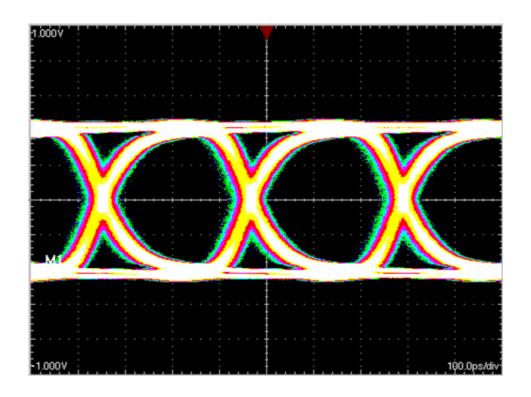

**Eye Diagram** at Transmitter

**Conditions**

- 3.125-Gbps Data Rate

- 40-Inch Trace Length

- PRBS 7 Data

- 0% Pre-Emphasis

- 85°C, VCC = 1.425 V

- **Receiver Equalization**

Bit Error Rate of 10<sup>-12</sup>

Tyco Backplane Connector

30"

**Eye Diagram** at Receiver

5"

### **Stratix GX Highlights**

- Second-Generation Product Reduces Customer Risk

- Long Distance Drive Capability

- Power-Efficient

- Hard DPA Makes it Easy

- Right Tools & Support

- Right Hard & Soft IP

- Complete Set of Efficient Hard IP Functions

- Significantly Reduces

Resource Consumption

# **Customer Engagement Plan**

### **Stratix GX Update**

- Stratix™ GX Silicon Characterization Exceeding Expectations

- Stratix GX Product Requires Much More than Silicon & Software

- Short-Term Factory Resources Prioritizing Product Completion

- Factory Resources Also Prioritizing Complete Protocol Support Packages

# **DPA & Source Synch TX**

X8 DPA Loopback Operates beyond 1 Gbps

TX Output Eye-Pattern at 1 Gbps

Preliminary Analysis Positive, Characterization Effort Is

**Ongoing**

#### **Transceiver Transmitter**

- Output Eye Pattern at 3.125 Gbps

- Output Voltage = 1 Volt

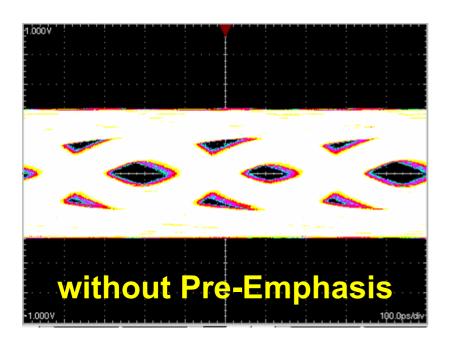

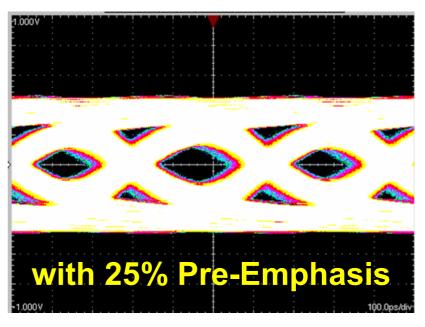

#### Signal through 40" Backplane

- Transceiver Output Eye-Pattern at 3.125 Gbps

- Output Voltage = 1 Volt

#### **Stratix GX Whole Product**

#### **Stratix GX Whole-Product Components**

Working Stratix GX Silicon

Advanced Quartus® II Design Support

Spice Simulation Package

**Device-Level Characterization & Documentation**

**Development Platform**

Protocol Characterization & Documentation

IP Cores & Reference Designs

App Notes & Board Design Guidelines

Interoperability Testing

**Backplane Characterization**

**Product Completion Top Priority for 1H-03**

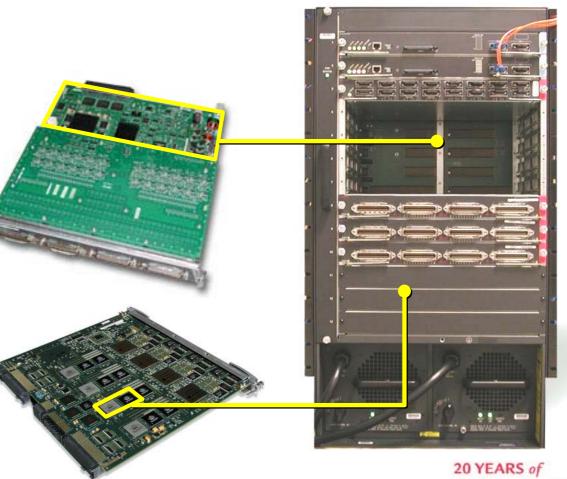

#### **Development Platform**

- Development Board

- Board Layout Guidelines

- Reference Designs

- Gerber Files

- Spice Models

- Software Support

- Much More . . .

Development Platform

Dramatically Improves Ease of Design

#### **Protocol Prioritization**

Relative Priority

10 Gigabit Ethernet XAUI

**SPI-4.2 with DPA**

**SONET/SDH Backplane**

Broadcast (SDI - SD/HD)

**Fibre Channel**

**Gigabit Ethernet**

**PCI Express**

Serial RapidIO

SFI-5

First Phase of Rollout Q1 to Q2 2003

Second Phase of Rollout Q2 to Q3 2003

2H-03

#### Stratix GX Deliverable Schedule

| Deliverable                                  | Date          |  |

|----------------------------------------------|---------------|--|

| Stratix GX Test Chip Characterization Report | January 2003  |  |

| Stratix GX Characterization Plan             | January 2003  |  |

| Stratix GX Characterization Regular Updates  | January 2003  |  |

| Stratix GX HSSI Spice Models                 | February 2003 |  |

| Stratix GX Development Board Functional Spec | February 2003 |  |

| Quartus II Compilation Support (No Pinouts)  | March 2003    |  |

| Stratix GX DPA Spice Models                  | March 2003    |  |

| Stratix GX Development Platform (\$20K)      | June 2003     |  |

| Full Support in Quartus II Version 3.0       | June 2003     |  |

#### Early Adopter Engagement Plan

- Customer / Field Completes Detailed Questionnaire

- Assess Customer Design Capability & Application (Protocol)

- Altera & Customer Decide if Opportunity Aligns with Stratix GX Schedule & Altera Support Capability

- Service-Level Disclosure with Customer

- Share Deliverables with Customers

#### Service-Level Disclosure

- Outlines Nature of Engagement with Customer

- Altera Commits to Providing Customer with Silicon, Support & Technical Details

- Customer Must Sign Non-Disclosure Agreement

- Customer Agrees to Accept Staged Information & Silicon Release

- Disclosure Clarifies Schedules on Remaining Device & Protocol-Characterization Effort & Collateral Plan

### **Engagement Guidelines**

- Customer Requirements to Start Engagement

- Sign Non-Disclosure Agreement

- Complete Questionnaire

- Commit to Purchase a Stratix GX

Development Platform

- Agree to Provide Feedback on Evaluation

Stratix GX Results

20 YEARS of