## Lab 6: SSN Decoder

- Create a four output combinational block that will recognize fields in your SSN

- SSN is three fields: XXX YY ZZZZ

- -F1 = 1 if input is equal to one of the numbers in the first group (XXX)

- -F2 = 1 if input is equal to one of the numbers in the 2nd group (YY)

- F3 = 1 if input is equal to one of the numbers in the 3rd group (ZZZZ)

- F4 = 1 if input is equal to numbers in any group

R 2/1/99

## Constraints

- Can only use 1 each of the following devices

- 7400 (4 two-input NANDs)

- 7402 (4 two-input NORs)

- 7404 (6 Inverters)

- 7408 (4 two-input AND)

- 7410 (3 three-input NAND)

- 7432 (4 two-input OR)

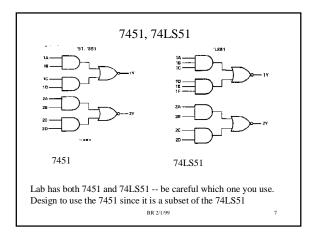

- 7451 (AND-OR-INVERT function)

- 7486 (4 two-input XOR gates)

BR 2/1/99

## What good is a 7451?

If a SOP equation has two product terms, with only two terms for each product term, then can implement with a 7451

If minimize ZEROS on K-Map, then get an SOP form for F'. The inverter on the output of the 7451 will convert it to F!!!

OR, can minimize '1's, then put an external inverter on the output of the 7451 to get the high true version.

BR 2/1/99

# Example for SSN= $458\,70\,2198$ Row ABCD F1 F2 F3 F4 0 0000 0 1 0 1 0 1 1 0001 0 0 1 1 1 2 0010 0 0 1 1 1 3 0011 0 0 0 1 1 5 0101 1 0 0 0 1 5 0101 1 0 0 0 1 6 0110 0 0 0 0 0 7 0111 0 1 0 1 0 1 8 1000 1 0 1 1 9 1001 0 0 1 1 10 1010 x x x x x 11 1011 x x x x x 12 1110 x x x x x 14 1110 x x x x x 15 1111 x x x x x BR 2/1/99

First Try: Minimize each map, ignore shared terms F1 F2 CD 00 01 11 10 00 0 1 X 1 01 0 1 X 0 01 0 0 X 0 11 0 0 X X 11 0 1 X X 10 0 0 X 10 0 0 X X F1 = BC' + AD' $F2 = \frac{BCD}{A'B'C'D'}$ BR 2/1/99

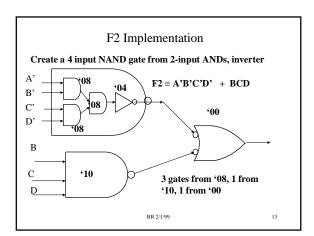

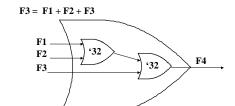

# An Implementation Will try to implement F1, F2, F3 directly, then implement F4 = F1 + F2 + F3 Need four inverters for A', B', C', D' F1 = BC' + AD' (use 7451 + inverter, this the 5th inverter) What about F2? F2 = A'B'C'D' + BCD Do NOT have a 4 input NAND gate????

## F4 Implementation

I used Nand-Nand implementation for SOP forms so that I could save the OR-gates in the '32 for this.

BR 2/1/99

### Final Gate Count

All gates from the '04 (6 inverters)

Part of the 7451

Three gates from the '08

One gate from the '10

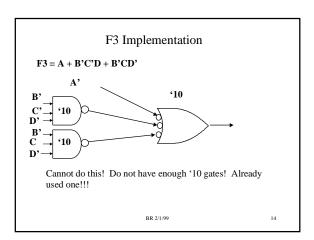

Three gates from the '10  $\,$

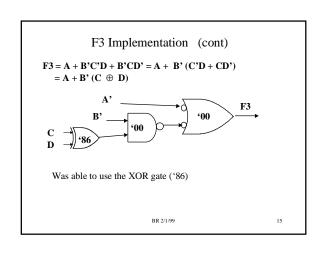

One gate from the '86

Two gates from the '32

There are MOST certainly other solutions....... Did not consider shared terms, did not minimize zeros. Many other avenues to try if these failed.

R 2/1/99

## Debugging

- Wire up ONE function at a time

- Start with whatever your simplest function is, then work towards hardest function.

- No need to proceed to next function until current one works

- If F1, F2, F3 all work, then getting F4 to work will be trivial.

- The TAs do NOT know what the correct solution is for your SSN! They will only be able to offer general debugging help.

BR 2/1/99

18